Išsamus SPI komunikacijos protokolo vadovas

Šiame straipsnyje išnagrinėsime išsamią serijinės periferinės sąsajos (SPI) protokolo informaciją, sutelkdami dėmesį į jo efektyvias duomenų perdavimo galimybes ir universalias programas.SPI yra greitas, sinchroninis ryšio protokolas, plačiai naudojamas įterptosiose sistemose, norint sujungti mikrovaldiklius su įvairiais periferiniais įrenginiais.Su savo pagrindinio vergo konfigūracija ir keturiomis pagrindinėmis linijomis-„Mosi“, „Mosi“, „SCLK“ ir „CS“-SPI supaprastina duomenų ryšį, užtikrinant sinchronizaciją įvairiuose įrenginiuose.Mes įsigilinsime į pagrindinius SPI principus, įskaitant jo veiklos dinamiką, aparatinės įrangos konfigūraciją, laiko diagramas ir praktinių sąrankos patarimus.Nesvarbu, ar dar nesate SPI, ar siekiate patobulinti savo supratimą, šis įrašas suteiks vertingų įžvalgų, kaip maksimaliai padidinti jo galimybes realiose programose.Katalogas

SPI protokolo apžvalga

Serijinėje periferinėje sąsajoje (SPI) naudojama 4 laidų sistema, kuri supaprastina CPU operacijas, sumažindama programinės įrangos pridėtines išlaidas.Žinomas dėl savo greičio ir efektyvumo, SPI yra pagrindinis įrenginiuose, tokiuose kaip AT91RM9200.Pagrindinio vergo sistemoje pagrindinis pagrindą valdo užduotis, sujungdamas su vergais per keturis reikalingus laidus: miso („Master in Slave Out“), „Mosi“ („Master Out Slave In“), SCLK (nuoseklusis laikrodis) ir CS (Chip Select).MISO linija nukreipia duomenis meistrui, o MOSI tvarko išeinančius duomenis.SCLK teikia „Master“ laikrodžių signalus, o CS palengvina įrenginio aktyvavimo valdymą.SPI paprastumas daro jį daugiausia naudingas norint sujungti kelis įrenginius vienoje magistralėje, vykdyti duomenų perdavimą nuosekliai ir pasiekti sinchronizaciją per laikrodžio impulsus.Čia meistras gali pristabdyti ryšį neturėdamas įtakos duomenų patikimumui.Nors SPI trūksta srauto valdymo ir duomenų patvirtinimo ypatybių, jo gebėjimas padidinti periferinius ryšius per išorinius dekoderius kompensuoja šiuos apribojimus.

Konkretūs SPI panaudojimo atvejai

SPI yra sukonstruotas aplink išskirtinę žiedinių autobusų sąranką, naudojant tokias dalis kaip SS (CS), SCK, SDI ir SDO, kad būtų galima keistis duomenimis.Pavyzdžiui, 8 bitų registro perdavimas naudoja laikrodžio kraštus duomenų judėjimui valdyti ir registruojant pamainas.Inicijavimas pagrindinio vergo sąrankoje prasideda nuo išankstinio sukonfigūruojančio siųstuvų-imtuvo buferių, iliustruojančių ryšio procesą.„Motorola's SPI“ išsiskiria sinchroniniu serijiniu ryšiu, naudodamas MOSI, MISO ir SCK, siekiant išplėstines siuntimo-atgavimo užduotis, lankstumą tarp pagrindinių vergų vaidmenų ir tvirtų laikrodžio funkcijų.Įrenginiai turi sinchronizuoti laikrodžio fazę ir poliškumą, kad būtų galima komunikacijos nuoseklumui.Gebant susieti iki 256 prievadų, SPI koncentruojasi į ryšį nuo taško iki taško ir paketinių duomenų perdavimo.

Vartotojo loginė formuluotė

Prisitaikančios vartotojo logikos projektavimas yra dinamiškas programoms, turinčioms kelių uostų struktūras.Dvigubo uosto konfigūracijoje nepriklausomi FIFOS tvarkomi duomenys, palyginti su prievado adresais.Tuo pačiu metu loginis arbitražas prižiūri duomenų perėjimą į SPI4 sąsają, pritaikant neatidėliotinus srauto valdymo duomenis ir FIFO būsenas.

SPI veiklos dinamika

SPI yra sukurtas patikimam ryšiui, kuriame pateikiami diskretiški duomenų kanalai ir transmisijos srauto valdymas.Didelis prievadų ryšys leidžia perduoti paketus pagrįstus duomenų perdavimą, užtikrinant patvirtinimą nuo taško iki taško per paketų adresus, taip išplėsti programos universalumą.

Duomenų perdavimo laiko diagramų tyrimas

SPI sąsajoms būdingos keturios laiko nustatymo schemos, atsižvelgiant į CPOL ir CPHA nustatymus.CPOL apibrėžia SCK tuščiosios eigos būseną, tuo tarpu CPHA nurodo mėginių ėmimo laikrodžio kraštą.Šios konfigūracijos yra aktyvios užtikrinant duomenų tikslumą ir sinchronizaciją.

Sinchroninis serijinis ryšys

„Motorola“ atsirado „Motorola“, SPI yra keturių laidų, dvikrypčių serijinių magistralių, sukurtų greitam sinchroniniam ryšiui, susiejant mikrovaldiklius su periferiniais įrenginiais, tokiais kaip EEPROM, RTC ir A/D keitikliai.SPI tinklas sumaniai jungia mišrius periferinius įrenginius, naudodama protokolus, kurie apeina tiesioginių, pilnų dvipusių mainų adresų mechanizmus.Papildomos eilutės, tokios kaip INT, gali pagerinti sistemos reagavimą.

Aparatūros konfigūracijos painiavos

Nepaisant SPI įgūdžių, susijusių su įvairiais periferiniais įrenginiais, individualūs kiekvieno įrenginio signalai suteikia sudėtingumo, palyginti su paprastesnėmis sistemomis, tokiomis kaip I2C.Šis sudėtingumas yra vidinis SPI aparatinės įrangos konfigūracijos aspektas, įtraukiantis „Shift Regist“ 8 bitų duomenų perdavimus.Veikimo metu įrenginiai saugiai keičia bitus per registrus, naudodamiesi laikrodžio krintančiu kraštu.

Gebėjimo ir praktiškumo vertinimas

Naudodamiesi tokiais elementais kaip „Spiclk“, „Mosi“, „Miso“ ir NSS, SPI tinklai nustato pagrindinio vergo vaidmenis, pagrįstus NSS PIN būsenomis.Palaikant vieną ar daugialypę aplinką, protokolas prisitaiko prie 16 periferinių įrenginių kontrolės.Nors jame trūksta srauto valdymo ir patvirtinimo metodų, protokolo struktūra efektyviai pritaiko įvairius ryšio sąrankas ir ryšius.

Sąrankos ir laiko iliustracijos

SPI duomenų operacijas reguliuoja tiesios laiko nustatymo taisyklės, kurioms įtakos turi SCK valdymas.Pavyzdžiui, kaip 10101010 registro modelis siunčia duomenis bitais per laikrodžio varomas pamainas, išryškindamas operatyvinį paprastumą ir duomenų perėjimo dinamiką žiedinės magistralėje.

Išplėstos įžvalgos apie spektaklį

Tinkamas SPI laikrodžio fazės ir poliškumo sinchronizavimas tarp pagrindinių ir vergų prietaisų naudojamas nuolatinėms duomenų operacijoms.Tokie parametrai kaip CPOL ir CPHA turėtų suderinti su SPI sujungtų sistemų įrenginiais, kad būtų palaikoma komunikacijos harmonija.

Praktinės sąrankos patarimai

SPI laikrodžio konfigūracijų koregavimai turi atsižvelgti į vergo įrenginio laikrodžio reikalavimus, kad būtų užtikrintas duomenų tikslumas perdavimo ciklų metu.Signalo kraštų atpažinimas duomenų perdavimo metu yra rimtas, kad būtų išvengta sujungimo neatitikimų.Produkto vadovai dažnai detalizuojami būtini parametrai, pabrėžiant tikslaus kritimo krašto suderinimo poveikį transmisijos tikslumui.

SPI komunikacijos pagrindai

Esant nuoseklioji periferinė sąsaja (SPI) yra visos dupleksinės sinchroninio serijinio ryšio protokolo, reikalaujančio iš anksto susitarti dėl sąveikos.Ši funkcija išskiria SPI iš esmės paryškinant sinchronizuotus mainus.Ryškus SPI aspektas yra jo priklausomybė nuo pagrindinio vergo modelio, kai pagrindinis įrenginys organizuoja valdymą, sukuriant laikrodžio signalus ir pradedant ryšių sesijas.Priešingai, vergų prietaisai lieka aiškiai suderinti su šiais signalais, kurie buvo pasirengę dalyvauti iškviesdami.

Kruopščiai organizuotas pagrindinio ir vergų prietaisų bendradarbiavimo mechanizmas tarp SPI.Meistras prisiima išskirtinę atsakomybę už laikrodžių valdymą, užtikrindamas nuolatinį duomenų mainų ritmą.Ši priežiūra supaprastina sinchronizaciją, pašalindama nenuspėjamumą, dažnai būnantį asinchroninėse sistemose.Nustatydami vieningą laiko nuorodą, abu įrenginiai gali tiksliai vykdyti operacijas, o praktika patobulinta per didelę programos patirtį.Tvarkingas SPI pobūdis pateikia efektyvias duomenų perdavimo galimybes, pateikiant tiesmukišką alternatyvą sudėtingesniems protokolams.

SPI sistema atskleidžia tam tikrus suvaržymus, ypač nustatymuose, kurie pabrėžia „Pug-and-Play“ lengvumą.Nelankstus jo protokolo pobūdis reiškia, kad suderinamumas turi būti kruopščiai išdėstytas iš anksto.Įrenginiai SPI konfigūracijos funkcijoje pagal laikrodžio signalus ir iš anksto nustatytus protokolo sutartis.Nors tai supaprastina sinchronizaciją, ji reikalauja pradinių sąrankos pastangų.Įgudęs šių principų pritaikymas parodė galimybę palengvinti bendravimo neatitikimus.Kaip pastebėta sesijos vertinimuose, SPI struktūrinio griežtumo suvokimas ne tik padidina praktinį diegimą, bet ir padidina taikymo tikslumą.

Apie mus

ALLELCO LIMITED

Skaityti daugiau

Greitas užklausa

Prašau atsiųsti užklausą, mes nedelsdami atsakysime.

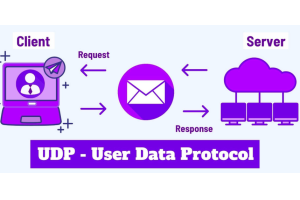

Viskas apie UDP: ryšio be ryšio vadovas

2024/12/30

HD technologija: vizualinės kompetencijos gerinimas

2024/12/30

Populiarūs įrašai

-

Sudėtingos instrukcijos Nustatykite kompiuterius: kaip jie pakeitė skaičiavimą?

8000/04/18 147749

-

USB-C PINOUT ir funkcijos

2000/04/18 111896

-

„Xilinx Unified“ modeliavimo primityvų naudojimas: išsamus FPGA projektavimo ir modeliavimo vadovas

1600/04/18 111349

-

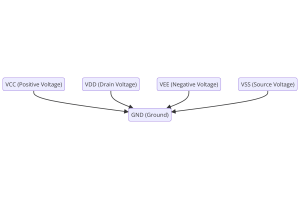

Maitinimo įtampa elektronikoje: VCC, VDD, VEE, VSS ir GND reikšmė

0400/04/18 83713

-

„RJ45“ jungties vadovas: „Pmout“, laidų, laidų tipai ir naudojimas

1970/01/1 79502

-

Pagrindinis vielos spalvų kodų vadovas šiuolaikinėse elektrinėse sistemose

Tai, kaip mūsų elektros sistemos naudoja spalvas, nėra tik išvaizdos.Kiekviena vielos spalva dabar rodo konkrečią funkciją, todėl montavimo ir priežiūros metu lengviau nustatyti ir tvarkyti elektro...1970/01/1 66866

-

Kokybės (Q) faktorius: lygtys ir programos

Kokybės koeficientas, arba „Q“, yra svarbus tikrinant, kaip gerai induktoriai ir rezonatoriai veikia elektroninėse sistemose, kuriose naudojami radijo dažniai (RF).„Q“ matuoja, kaip gerai grandinė ...1970/01/1 63002

-

Išvalymo vožtuvo vadovas: funkcija, simptomai, testavimas ir pakeitimas, kad būtų galima optimaliai atlikti variklio veikimą

Išvalymo vožtuvas yra pagrindinė automobilio sistemos dalis, padedanti išlaikyti orą švarų, valdant degalų garus, kol jie gali ištrūkti į atmosferą.Tai ne tik padeda aplinkai sumažinti taršą, bet i...1970/01/1 62932

-

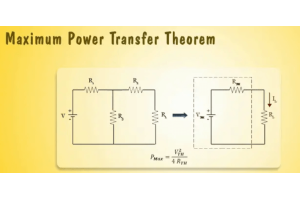

Pasiekti maksimalų našumą naudojant maksimalios galios perdavimo teoremą

Maksimalios galios perdavimo teorema paaiškina, kaip energija iš šaltinio, pavyzdžiui, akumuliatorius ar generatorius, teka į prijungtą apkrovą.Tai parodo tikslią sąlygą, kai apkrova gauna daugiaus...1970/01/1 54073

-

A23 akumuliatoriaus specifikacijos ir suderinamumas

„A23“ baterija yra maža, cilindro formos akumuliatorius, turintis aukštą įtampą.Taip pat vadinamas 23A, 23AE arba MN21, jis veikia esant 12 voltų ir daug aukštesnis nei AA ar AAA baterijos...1970/01/1 52087