CPLD paaiškino: programuojamų loginių įrenginių vadovas

Dinaminiame elektroninio dizaino pasaulyje sudėtingi programuojami loginiai įrenginiai (CPLDS) išsiskiria kaip universalūs įrankiai, sklandžiai maišant pritaikomumą, tikslumą ir efektyvumą.Šie prietaisai revoliucionavo grandinės dizainą, įvedant programuojamas makro ląsteles ir dominuojančią sujungimo matricą, leidžiančią sukurti sudėtingas logines funkcijas, turinčias nepaprastą patikimumą.Nuo pat įkūrimo devintajame dešimtmetyje iki pagrindinio vaidmens šiuolaikinėse pramonės šakose, tokiose kaip tinklų kūrimas, automobilių ir kosmoso sritys, CPLDS įrodė, kad jums reikia tiek lankstumo, tiek našumo.Šis straipsnis įsigilina į CPLDS kelionę, jų išskirtines savybes, praktines programas ir programavimo metodikas, kurios daro jas kertiniu akmeniu skaitmeninės logikos dizaine.Katalogas

CPLD apžvalga

Sudėtingų programuojamų loginių prietaisų (CPLDS) viešpatavime atrandamas modernus programuojamų loginių makro ląstelių gobelenas, susipynusias per dominuojančią sujungimo matricą.Šios makrokomandos ląstelės (MC) ir įvesties/išvesties (I/O) vienetų linijos leidžia jums griežtai suprojektuoti grandines, sukonfigūruojant unikalių funkcijų struktūras.Skirtingai nuo prietaisų, kurie yra suglumę dėl sudėtingo sujungimo laiko, CPLD naudoja nejudinamus metalinius laidus.Ši savybė jiems suteikia nuoseklų ir numatomą laikrodžio elgesį, todėl laiko prognozės tampa patikimesnės ir tikslesnės.

Kelionė ir panaudojimas

Aštuntajame dešimtmetyje paskelbė programuojamų loginių prietaisų (PLD) atsiradimą, skatinant pereiti prie programuojamų makrokomandų vienetų.Šis poslinkis sukūrė didelį dizaino lankstumą, išskiriantį juos nuo statinių skaitmeninių grandinių, nors iš pradžių jų naudingumas buvo suvaržytas paprastesnėms grandinėms.CPLD atsiradimas devintojo dešimtmečio viduryje pakeitė šį kraštovaizdį, sudarydamas kelią sudėtingoms grandinės dizainams.Nuo to laiko jie įsitraukė į pramonės šakų, tokių kaip tinklų kūrimas, automobilių elektronika, CNC apdirbimas ir aviacijos ir kosmoso sistemos, audinį.Galite prisiminti apie tai, kaip CPLDS supaprastinti procesai, kurie kadaise reikalavo kruopštaus rankinio darbo, pažymėdami nepaprastą efektyvumo šuolį.

Išskirtinės CPLDS savybės

CPLDS išsiskiria per savo pritaikomą programavimą, plačią integraciją, greitų plėtros galimybes ir plataus masto pritaikomumą kartu su ekonominėmis gamybos sąnaudomis.Jie patinka tiems, kurie turi minimalią aparatūros patirtį, tarnaudami kaip patikimi ir saugūs produktai, kuriems nereikia atlikti išsamius bandymus.Kaip jų meistriškumo liudijimas didelio masto grandinės dizaine, CPLD vaidina pagrindinį vaidmenį kuriant prototipą ir tarnauja žemiau 10 000 vienetų, įkūnijant jums naudingą kompetenciją.Tinkamumas, kuriuo CPLDS prisitaiko prie besikeičiančių projekto reikalavimų, dažnai pelno jiems įvertinimą, pabrėždamas jų faktinį universalumą dinaminėje aplinkoje.

Taikymo metodai

Šios integruotos grandinės leidžia išsiaiškinti logines funkcijas, pritaikytas jų poreikiams, naudojant schemas ir aparatinės įrangos aprašymo kalbas kūrimo platformose.Pavyzdžiui, projektuojant atsakiklį, schemos ir aparatinės įrangos aprašymai yra paruošti ir sudaromi kompiuteryje.Naudojant atsisiuntimo laidą, kodas perkeliamas į CPLD programavimui sistemoje, kurią sudaro bandymai, trikčių šalinimas ir dizaino tobulinimas.Tada sėkmingai paruošti dizainai yra masiškai gaminami atkartojant CPLD lustus.Projektuose, tokiuose kaip šviesoforo sistemos, projektavimo proceso pakartojimas tampa būtinas, panašiai kaip namo atkūrimas, kad būtų atkurtas jo naujumas.Ši pasikartojanti metodika dažnai sudaro pagrindą įsisavinti, skatinti įgūdžius ir pasitikėjimą savimi.

Pagrindiniai variantai

Per daugelį metų tokios įmonės kaip „Altera“, „Lattice“ ir „Xilinx“ pristatė garsias CPLDS linijas.Pažymėtini pavyzdžiai yra „Altera“ EPM7128S, Grotelės LC4128V, ir Xilinx's XC95108 .Šie modeliai rado svarbų vaidmenį įvairiose globaliose programose.Tie, kuriems buvo suteikta privilegija dirbti su šiais skirtingais produktais, dažnai pastebi subtilius, tačiau galingus skirtumus, optimizuojančius tam tikras funkcijas.Tai atspindi puikios atrankos procesą, kuriam įtakos turi konkretūs projekto reikalavimai, kai kiekvienas variantas yra unikalus patrauklumas.

FPGA ir CPLD identifikavimas ir klasifikavimas

|

Aspektas |

Cpld |

FPGA |

|

Loginis elgesio formavimas |

Formos loginis elgesys naudojant produkto termino struktūrą.

Pavyzdžiai: „Gretice ISPLSI“ serija, „Xilinx XC9500“ serija, „Altera Max7000s“

serija, gardelės Macho serija |

Formos loginis elgesys naudojant lentelės paieškos metodą.

Pavyzdžiai: „Xilinx Spartan“ serija, „Altera Flex10K“, „ACEX1K“ serija |

|

Tinkamumas |

Tinka algoritmams ir derinio logikai, veikia

geriau su ribotais trigeriais ir turtingais produkto terminais |

Tinka nuosekliajai logikai, geriau veikia

struktūros, kuriose gausu trigerių |

|

Laiko vėlavimas |

Nuolatinė laidų struktūra suteikia vienodą ir

Numatomas laiko vėlavimas |

Segmentinė laidų struktūra lemia nenuspėjamą laiką

vėlavimai |

|

Programavimo lankstumas |

Fiksuotos vidinės grandinės yra modifikuotos programavimui.

Naudojamas loginis bloko lygio programavimas |

Vidinis laidas modifikuotas programavimui.Logika

Vartų lygio programavimas suteikia didesnį lankstumą |

|

Integracija |

Mažesnė integracija, palyginti su FPGA |

Didesnė integracija su sudėtingesne laidų struktūra ir

Logikos įgyvendinimas |

|

Paprastas naudojimas |

Lengviau naudoti naudojant programavimą naudojant „E2PROM“ arba „FastFlash“.

Nereikia išorinės atminties mikroschemos |

Norint saugoti programavimą, reikia išorinės atminties

Informacija, todėl sudėtingesnis naudojimas |

|

Greitis ir nuspėjamumas |

Greitesnis greitis ir geresnis laiko nuspėjamumas dėl

Loginių blokų sujungimas |

Lėtesnis greitis ir mažiau nuspėjamas laikas dėl

Vartų lygio programavimas ir paskirstytas sujungimas |

|

Programavimo technologija |

Naudoja „E2PROM“ arba „Flash“ atminties programavimą.Programavimo duomenys

išlaikoma, kai sistema išjungta.Palaiko programavimą a

programuotojas arba sistemoje |

Remiantis SRAM programavimu.Programavimo duomenys prarandami, kai

Sistema išjungta ir turi būti perkrauta.Palaiko dinamiką

konfigūracija |

|

Konfidencialumas |

Siūlo geresnį konfidencialumą |

Suteikia mažesnį konfidencialumą |

|

Energijos suvartojimas |

Paprastai didesnė energijos suvartojimas, ypač su

Aukštesnė integracija |

Mažesnis energijos suvartojimas, palyginti su CPLD |

CPLD programavimo kalbos

Išanalizavus, kaip programuojami sudėtingi programuojami loginiai įrenginiai (CPLD) yra kertinis akmuo kuriant universalius aparatūros sprendimus.Istoriniai CPLD programavimo metodai rėmėsi kopėčių diagramomis arba aparatinės įrangos aprašymo kalbomis (HDLS), o „Verilog HDL“ ir „VHDL“ yra vyraujantys pasirinkimai.Pasirinkta kalba gali formuoti ir projektavimo strategiją, ir įgyvendinimo efektyvumą.

• Verilog HDL: „Verilog HDL“ puoselėja savo paprastas sintaksės ir tvirtas modeliavimo galimybes, atspindinčias metodikas, naudojamas skaitmeninės logikos dizaine.Jos integracija su elektroninio projektavimo automatizavimo (EDA) įrankiais leidžia sklandžiai atlikti sintezę ir modeliavimą.Pastebėta, kad C Verilog sintaksė sumažina kliūtį patekti į programą, turinčią programų foną, padidindami kelionę nuo dizaino iki dislokavimo įvairiuose pramonės sektoriuose.

• VHDL: VHDL suteikia sudėtingesnį ir išraiškingesnį DTL programavimo variantą.Dažnai yra projektų pasirinkimas, reikalaujantis kruopštaus dokumentacijos ir griežto tipo tikrinimo, bruožų, vertinamų aviacijos ir gynybos pramonėje.Galite pastebėti, kad nepaisant galimo VHDL sudėtingumo mažesniuose projektuose, jos drausminga struktūra palaiko išskirtinai patikimų dizainų sukūrimą, būtinybę toje aplinkoje, kurioje dominuoja saugumas.

Apie mus

ALLELCO LIMITED

Skaityti daugiau

Greitas užklausa

Prašau atsiųsti užklausą, mes nedelsdami atsakysime.

NMOS tranzistoriai: dizainas, veikimas ir programos

2024/12/29

Greitas Furjė transformacija (FFT): revoliucija skaitmeninio signalo apdorojimas

2024/12/29

Populiarūs įrašai

-

Sudėtingos instrukcijos Nustatykite kompiuterius: kaip jie pakeitė skaičiavimą?

8000/04/18 147778

-

USB-C PINOUT ir funkcijos

2000/04/18 112035

-

„Xilinx Unified“ modeliavimo primityvų naudojimas: išsamus FPGA projektavimo ir modeliavimo vadovas

1600/04/18 111352

-

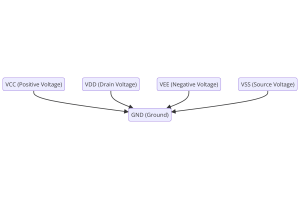

Maitinimo įtampa elektronikoje: VCC, VDD, VEE, VSS ir GND reikšmė

0400/04/18 83792

-

„RJ45“ jungties vadovas: „Pmout“, laidų, laidų tipai ir naudojimas

1970/01/1 79602

-

Pagrindinis vielos spalvų kodų vadovas šiuolaikinėse elektrinėse sistemose

Tai, kaip mūsų elektros sistemos naudoja spalvas, nėra tik išvaizdos.Kiekviena vielos spalva dabar rodo konkrečią funkciją, todėl montavimo ir priežiūros metu lengviau nustatyti ir tvarkyti elektro...1970/01/1 66976

-

Išvalymo vožtuvo vadovas: funkcija, simptomai, testavimas ir pakeitimas, kad būtų galima optimaliai atlikti variklio veikimą

Išvalymo vožtuvas yra pagrindinė automobilio sistemos dalis, padedanti išlaikyti orą švarų, valdant degalų garus, kol jie gali ištrūkti į atmosferą.Tai ne tik padeda aplinkai sumažinti taršą, bet i...1970/01/1 63111

-

Kokybės (Q) faktorius: lygtys ir programos

Kokybės koeficientas, arba „Q“, yra svarbus tikrinant, kaip gerai induktoriai ir rezonatoriai veikia elektroninėse sistemose, kuriose naudojami radijo dažniai (RF).„Q“ matuoja, kaip gerai grandinė ...1970/01/1 63044

-

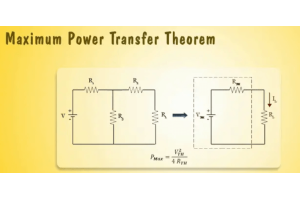

Pasiekti maksimalų našumą naudojant maksimalios galios perdavimo teoremą

Maksimalios galios perdavimo teorema paaiškina, kaip energija iš šaltinio, pavyzdžiui, akumuliatorius ar generatorius, teka į prijungtą apkrovą.Tai parodo tikslią sąlygą, kai apkrova gauna daugiaus...1970/01/1 54097

-

A23 akumuliatoriaus specifikacijos ir suderinamumas

„A23“ baterija yra maža, cilindro formos akumuliatorius, turintis aukštą įtampą.Taip pat vadinamas 23A, 23AE arba MN21, jis veikia esant 12 voltų ir daug aukštesnis nei AA ar AAA baterijos...1970/01/1 52198