Skaitmeninės fazės užrakinta kilpa (DPLL): dizainas, komponentai ir operacijos

Šis vadovas tiria skaitmeninės fazės užrakintą kilpą (DPLL)-pagrindinė šiuolaikinių skaitmeninių grandinių, žinomų dėl savo tikslumo ir patikimumo, dalis.DPLL vaidina tokias užduotis kaip moduliacija, demoduliacija ir sinchronizacija įvairiose pramonės šakose.Suskirstydamas savo komponentus ir kaip jis veikia, šis straipsnis pabrėžia DPLL dizainą, funkcijas ir pranašumus, palyginti su tradicinėmis analoginėmis sistemomis.Katalogas

Įrangos tyrinėjimas

Skaitmeninės fazės užrakinta kilpa (DPLL) yra esminis šiuolaikinės technologijos elementas, kurį lemia skaitmeninės grandinės technologijos proveržiai.Jo universalūs pritaikymai apima moduliaciją, demoduliaciją, dažnio sintezę, FM stereo dekodavimą, spalvų subkaratorių sinchronizavimą ir vaizdo apdorojimą.Šie prietaisai spindi dėl jų patikimumo, kompaktiškumo ir ekonomiškumo, veiksmingai įveikdami būdingus analoginių fazių užrakintų kilpų trūkumus, tokius kaip DC dreifas, prietaiso prisotinimas ir jautrumas galios bei temperatūros svyravimams.Galimybė efektyviai valdyti atskirus pavyzdžius prisideda prie plačiai paplitusio priėmimo.Vienareikšmiškai fazės užrakinta kilpa veikia kaip fazės grįžtamojo ryšio valdymo sistema, o DPLL įrodo pranašesnę, naudojant diskretinius skaitmeninius signalus klaidoms valdyti, o ne ištisinės analoginės įtampos, todėl aprašymas yra visos skaitmeninės fazės užrakintos kilpos (DPLL).

DPLL sudaro komponentai: fazės atskaitos ekstrahavimo grandinė, kristalų osciliatorius, dažnio daliklis, fazių lygintuvas ir impulsų kompensavimo vartai.Dažnio daliklio išėjimas suderinamas su norimu dažniu, nes fazės lygintuvas atidžiai tikrina etaloninį signalą.Jei pastebimas didesnis vietinis dažnis, impulsai yra strategiškai pašalinami, kad būtų sumažintas dažnis, tuo tarpu jei dažnis yra nepakankamas, impulsai pridedami, kad būtų galima patikslinti sinchronizaciją.Stiprią DPLL sudaro skaitmeninės fazės detektorius (DPD), skaitmeninio kilpos filtras (DLF) ir skaitmeninės įtampos kontroliuojamas osciliatorius (DCO).Ilgus metus trukusių eksperimentų ir pritaikymo inžinieriai paskatino atskleisti plačias DPLL galimybes įvairiose pramoninėse srityse, suteikdami gilias įžvalgas apie jų veiklą ir patobulinimą.

Skaitmeninės fazės detektorius (DPD)

Pagrindinis DPLL komponentas yra skaitmeninės fazės detektorius, dar žinomas kaip mėginių ėmimo fazės detektorius, norint palyginti įvesties signalo fazę su išėjimo iš įtampos kontroliuojamo generatoriaus išėjimu.Gauta išėjimo įtampa, atspindinti fazės diferencialą, vadovauja kilpos reguliavimo procesams.Skaitmeninių fazių detektoriai būna įvairių rūšių: nulinio perėjimo, flip-flop, švino-lag ir Nyquist greičio imčių detektorių.

Skaitmeninės kilpos filtras (DLF)

Skaitmeninės kilpos filtras vaidina svarbų vaidmenį mažinant triukšmą ir tobulinant kilpos reakcijos laiką.Jo, kaip taisomojo elemento, funkcija yra reikšminga, pakartodama jo analoginių kolegų pareigą.Sąmoningas skaitmeninio filtro struktūros dizainas ir pasirinkimas yra svarbus suteikiant DPLL galią siekti jo veikimo tikslų.

Skaitmeninės įtampos valdomas osciliatorius (DCO)

Skaitmeninis įtampos valdomas osciliatorius, kartais vadinamas skaitmeniniu laikrodžiu, veikia panašiai kaip analoginis VCO, sukuriantis išvestį kaip impulsų seką.DLF valdo šių impulsų laiką, siųsdamas reguliavimo signalus, darant įtaką vėlesniam mėginių ėmimo laikotarpiui, palyginti su ankstesniais pakeitimais.Ši iteracinio grįžtamojo ryšio kilpa buvo patobulinta tiek empiriniais tyrimais, tiek teoriniais patobulinimais, sukūrusiu daugybės šiuolaikinių programų pagrindą.

Skaitmeninės fazės užrakintos kilpos operacijos

Skaitmeninės fazės užrakinta kilpa atliekamas kruopštus procesas, skirtas kruopščiai sinchronizuoti dažnius:

Signalo palyginimo dinamika

Iš pradžių įvesties signalas ir vietinis osciliatoriaus signalas, suprantamas kaip sinusas ir kosinusas, įveda į skaitmeninės fazės detektoriaus vertinimo etapą.Detektorius suteikia išėjimo įtampą, atspindinčią šių signalų fazės neatitikimą.Šis fazių palyginimas yra panašus į sudėtingą muzikos instrumento derinimo procesą, reikalaujantį koreguoti, kad būtų išlaikyta harmoninga simetrijos ir tikslumo pusiausvyra.

Dažnio reguliavimo procesas

Vėliau skaitmeninio kilpos filtras įgauna sumaniai išvalyti detektoriaus aukšto dažnio triukšmo išėjimą.Šis poliruotas signalas sureguliuoja DCO (skaitmeniniu būdu valdomą osciliatoriaus) įvesties įtampą, subtiliai paveikdama vietinio osciliatoriaus dažnį.Kreipiant dėmesį į bet kokius dažnio neatitikimus, sistema naudoja žemo dažnio filtrą, kuris leidžia DCO patekti į lygiavertį.Šis adaptyvusis mechanizmas atspindi nuolatinį budrumą, randamą sudėtingoje aplinkoje, tokioje kaip oro eismo valdymas, kur nuolatinis tobulinimas užtikrina sklandžias operacijas.

Sinchronizacijos pasiekimai ir priežiūra

Kai vietinis osciliatoriaus signalas atitinka įvesties dažnį, fazių skirtumas panaikina, sukuriant nuoseklų nuolatinės srovės išvestį tiek iš fazių detektoriaus, tiek kilpos filtro.Stabilizuodamas jo dažnį, DCO veda kilpą į sinchronizuotą „užrakinta būseną“.Ši pusiausvyra liudija kilpos derybą dėl nuoseklumo, primenant stabilią energijos tinklų funkcionalumą, reikalaujantį nuolatinės sinchronizacijos, kad būtų išvengta chaoso.Išsamus šios procedūros progresas pabrėžia skaitmeninės fazės užrakintos kilpos vaidmenį technologinėse sistemose, įgudęs pasiekti sinchronizaciją kintančiomis sąlygomis.

Apie mus

ALLELCO LIMITED

Skaityti daugiau

Greitas užklausa

Prašau atsiųsti užklausą, mes nedelsdami atsakysime.

Branduolio architektūros evoliucija ir klasifikacija

2025/01/7

Išsamus „Testbenches“ vadovas: Skaitmeninės sistemos patikrinimo įrankiai ir metodai

2025/01/7

Populiarūs įrašai

-

Sudėtingos instrukcijos Nustatykite kompiuterius: kaip jie pakeitė skaičiavimą?

8000/04/18 147749

-

USB-C PINOUT ir funkcijos

2000/04/18 111907

-

„Xilinx Unified“ modeliavimo primityvų naudojimas: išsamus FPGA projektavimo ir modeliavimo vadovas

1600/04/18 111349

-

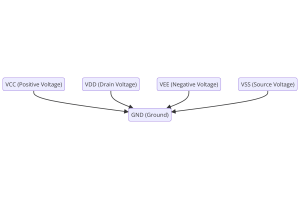

Maitinimo įtampa elektronikoje: VCC, VDD, VEE, VSS ir GND reikšmė

0400/04/18 83714

-

„RJ45“ jungties vadovas: „Pmout“, laidų, laidų tipai ir naudojimas

1970/01/1 79502

-

Pagrindinis vielos spalvų kodų vadovas šiuolaikinėse elektrinėse sistemose

Tai, kaip mūsų elektros sistemos naudoja spalvas, nėra tik išvaizdos.Kiekviena vielos spalva dabar rodo konkrečią funkciją, todėl montavimo ir priežiūros metu lengviau nustatyti ir tvarkyti elektro...1970/01/1 66869

-

Kokybės (Q) faktorius: lygtys ir programos

Kokybės koeficientas, arba „Q“, yra svarbus tikrinant, kaip gerai induktoriai ir rezonatoriai veikia elektroninėse sistemose, kuriose naudojami radijo dažniai (RF).„Q“ matuoja, kaip gerai grandinė ...1970/01/1 63004

-

Išvalymo vožtuvo vadovas: funkcija, simptomai, testavimas ir pakeitimas, kad būtų galima optimaliai atlikti variklio veikimą

Išvalymo vožtuvas yra pagrindinė automobilio sistemos dalis, padedanti išlaikyti orą švarų, valdant degalų garus, kol jie gali ištrūkti į atmosferą.Tai ne tik padeda aplinkai sumažinti taršą, bet i...1970/01/1 62947

-

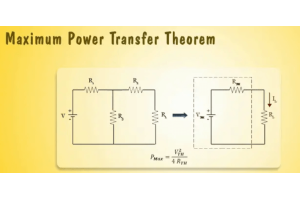

Pasiekti maksimalų našumą naudojant maksimalios galios perdavimo teoremą

Maksimalios galios perdavimo teorema paaiškina, kaip energija iš šaltinio, pavyzdžiui, akumuliatorius ar generatorius, teka į prijungtą apkrovą.Tai parodo tikslią sąlygą, kai apkrova gauna daugiaus...1970/01/1 54077

-

A23 akumuliatoriaus specifikacijos ir suderinamumas

„A23“ baterija yra maža, cilindro formos akumuliatorius, turintis aukštą įtampą.Taip pat vadinamas 23A, 23AE arba MN21, jis veikia esant 12 voltų ir daug aukštesnis nei AA ar AAA baterijos...1970/01/1 52088