EP2S60F672C4 FPGA: funkcijos, programos, programavimo ir duomenų lapų vadovas

Šiame vadove gausite aiškią „EP2S60F672C4“, galingas FPGA iš „Intel's Stratix II“ šeimos, apžvalgą.Sužinosite apie jo pagrindines savybes, architektūrą, bloko struktūrą ir technines specifikacijas, kad suprastumėte, kaip jis tinka pažangių skaitmeninių dizainų.Tai taip pat apima jūsų programavimo veiksmus, programas, pranašumus ir trūkumus, kad galėtumėte tiksliai pamatyti, kur ir kaip galima naudoti šį įrenginį.Katalogas

Kas yra EP2S60F672C4?

EP2S60F672C4 yra didelio tankio FPGA iš „Intel“ (buvusi „Altera“), priklausanti Stratix II šeimai.Pastatytas ant 90 nm, 1,2 V vario SRAM proceso, jis suteikia didelę loginę talpą 672 kamuolių FBGA pakete, todėl jis yra idealus sudėtingoms skaitmeninėms sistemoms.Kaip „EP2S“ serijos dalis, „60“ įrenginys yra „Stratix II“ serijos viduryje ir viršutiniame diapazone, siūlantis stiprų loginio tankio, įterptos atminties ir I/O išteklių balansą.Žinomas dėl tvirtos architektūros ir patikimumo, ši FPGA išlieka patikimas pasirinkimas daugelyje pažangių dizainų.

Ieškote EP2S60F672C4?Susisiekite su mumis, kad patikrintumėte dabartines akcijas, pristatymo laiką ir kainą.

EP2S60F672C4 CAD modeliai

EP2S60F672C4 simbolis

EP2S60F672C4 pėdsakas

EP2S60F672C4 3D modelis

EP2S60F672C4 funkcijos

• Išplėstinis 90 nm, 1,2 V CMOS procesas

EP2S60F672C4 yra pagamintas 90 nm visų sluoksnio vario CMOS procese, kuris veikia esant 1,2 V šerdies įtampai.Ši technologija įgalina didelį greitį, sumažėjusį energijos suvartojimą ir didesnį loginio tankį, palyginti su senesnėmis FPGA kartomis.

• Adaptive logikos modulio (ALM) architektūra

Įrenginys naudoja išmaldą kaip savo loginį statybinį bloką, o ne tradicinius loginius elementus.Ši architektūra pagerina išteklių panaudojimą, leidžiančią efektyviai įgyvendinti sudėtingesnes logines funkcijas toje pačioje silicio srityje.

• Didelis loginis tankis

Su maždaug 60 440 loginių elementų (24 176 alms) FPGA palaiko didelius ir modernius skaitmeninius dizainus.Dėl šios didelės talpos jis tinka tokioms programoms kaip signalo apdorojimas, ryšiai ir įterptosios valdymo sistemos.

• „Trimatrix ™“ mikroschemos atmintis

EP2S60F672C4 integruoja trijų tipų RAM blokus (M512, M4K ir M-RAM), kad iš viso būtų apie 2,4 MBIT įterptos atminties.Šis derinys leidžia efektyviai įdiegti mažus FIFO, vidutinius buferius ir didelius dviejų uostų prisiminimus.

• Dedikuoti DSP blokai

Įrenginį sudaro 36 specialūs DSP blokai, skirti aritmetinėms operacijoms, tokioms kaip daugybos, kaupimosi ir FIR filtravimas.Šie blokai padidina skaičiavimo reikalaujančių užduočių našumą, išsaugant bendruosius loginius išteklius.

• Greitaeigis I/O ir signalo vientisumas

Jis palaiko įvairius vienos rūšies ir diferencialinius I/O standartus kartu su dinaminio fazės suderinimo (DPA) grandine.Šios savybės įgalina stabilius, spartų duomenų perdavimą iki 1 Gbps, užtikrinant patikimą ryšį su išoriniais komponentais.

• Turtinga išorinės atminties sąsajos palaikymas

FPGA yra suderinamas su DDR, DDR2, QDR II, RLDRAM II ir kitais atminties standartais.Integruota sąsajos palaikymas supaprastina plokštės dizainą ir pasiekia didelį duomenų pralaidumą atminties reikalaujančioms programoms.

• Lankstus laikrodžio valdymas

Iki 12 lustų PLL leidžia dauginti laikrodį, padalijimą, fazių perjungimą ir perjungimą be gedimų.Galite tiksliai sureguliuoti laikrodžio domenus ir sumažinti virpesius, palaikydami vidinį laikrodžio dažnį iki 500–550 MHz.

• „Bitstream“ šifravimas ir pertvarkymas

EP2S60F672C4 palaiko AES pagrįstą „BitsStream“ šifravimą, kad būtų užtikrinta intelektinė nuosavybė.Tai taip pat siūlo nuotolinio pertvarkymo galimybes, įgalinančias atnaujinimus lauke, nepakeičiant įrenginio.

„Stratix II“ bloko diagrama

„Stratix II“ bloko diagrama, kaip parodyta EP2S60F672C4, iliustruoja vidinį logikos, atminties ir DSP išteklių išdėstymą, kuris sudaro FPGA branduolį.Logikos masyvo blokai (laboratorijos) yra išdėstyti įprastame tinklelyje, apsuptas įterptų RAM ir DSP stulpelių, kurie suteikia greitas aritmetines ir lusto laikymo galimybes.Periferiniai I/O elementai ir laikrodžių tinklai nustato šią struktūrą, įgalinant efektyvų duomenų perdavimo ir laiko valdymą tarp FPGA ir išorinių įrenginių.Ši diagrama yra svarbi, nes ji padeda suprasti, kaip skirtingi funkciniai blokai yra fiziškai organizuoti, leidžiant jiems optimizuoti išdėstymą, maršruto parinkimą ir bendrą sistemos veikimą.

„Stratix II I/O Banks“ diagrama

Ši „Stratix II I/O Banks“ diagrama iliustruoja, kaip yra sugrupuoti EP2S60F672C4 įvesties/išvesties kaiščiai ir kokius elektros standartus palaiko kiekviena grupė.Kiekvienas I/O bankas yra skirtas valdyti konkrečius įtampos lygius, signalizacijos tipus ir tokias funkcijas kaip LVTTL, SSTL, LVDS arba laikrodžio įvesties standartai.Išdėstymas parodo, kaip skirtingi bankai (pvz., 1, 2, 5, 6, palyginti su 3, 4, 7, 8 ir kt.) Yra optimizuoti bendrosios paskirties I/O arba greitaeigių diferencialinių signalų signalizacijai, įskaitant LVDS/LVPECL laikrodžio įėjimus kraštuose.Suprasti šią struktūrą svarbu priskiriant kaiščius, nes tinkamas banko pasirinkimas užtikrina elektrinį suderinamumą, supaprastina lentos maršrutą ir maksimaliai padidina FPGA našumą didelės spartos dizaine.

EP2S60F672C4 specifikacijos

|

Tipas |

Parametras |

|

Gamintojas |

Altera/intel |

|

Serija |

„Stratix® II“ |

|

Pakuotė |

Dėklas |

|

Dalies būsena |

Pasenęs |

|

Laboratorijų/CLB skaičius |

3022 |

|

Loginių elementų/ląstelių skaičius |

60,440 |

|

Iš viso RAM bitai |

2 544,192 |

|

I/O skaičius |

492 |

|

Įtampa - tiekimas |

1,15 V ~ 1,25 V |

|

Montavimo tipas |

Paviršiaus laikiklis |

|

Darbinė temperatūra |

0 ° C ~ 85 ° C (TJ) |

|

Paketas / atvejis |

672-BBGA |

|

Tiekėjo įrenginių paketas |

672-FBGA (27 × 27) |

|

Bazinis produkto numeris |

EP2S60 |

EP2S60F672C4 programos

1. Skaitmeninio signalo apdorojimas (DSP) ir filtravimas

EP2S60F672C4 puikiai tinka įgyvendinti aukštos kokybės DSP funkcijas, tokias kaip FIR ir IIR filtrai, FFT apdorojimas ir sudėtingos aritmetinės operacijos.Jo skirti DSP blokai efektyviai tvarko daugybinius ir kaupimus, atlaisvindami bendrąsias loginius išteklius kitoms užduotims.„On-Chip Trimatrix ™“ atmintis leidžia sklandų duomenų buferinį ir vamzdyną, o tai puikiai tinka apdoroti realiuoju laiku esant aukštam imčių greičiui.Tai daro įrenginį idealų patobulintoms garso, vaizdo ir radaro signalo programoms.

2. Greita komunikacija ir tinklų kūrimas

FPGA greitaeigė I/O sąsajos ir dinaminės fazės derinimo (DPA) grandinės palaikymas patikimas, gigabit lygio duomenų perdavimas.Tai gali įgyvendinti komunikacijos protokolus ir fizinio sluoksnio funkcijas tokioms sistemoms kaip maršrutizatoriai, jungikliai ir galinės plokštumos sujungimai.Turėdamas didelę loginę talpą ir lanksčius PLL, jis gali valdyti sudėtingą laiką ir protokolo konversijas tarp kelių greitųjų sąsajų.Šios galimybės daro tai labai tinkama telekomunikacijų infrastruktūrai ir didelio juostos pločio tinklų įrangai.

3. Atminties valdikliai ir duomenų apdorojimo sistemos

EP2S60F672C4 palaiko įvairias išorinių atminties sąsajas, įskaitant DDR, DDR2, RLDRAM II ir QDR II, todėl ji yra ideali projektuoti aukšto lygio atminties valdiklius.Tai gali valdyti duomenų buferinį, adresų generavimą ir arbitražą dideliu greičiu, kurio vėlavimas yra minimalus.Greito laikrodžio tinklų ir įterptųjų RAM blokų derinys leidžia efektyviai valdyti didelius duomenų srautus.Tai daro FPGA tinkamą vaizdo apdorojimui, vaizdo transliacijai ir moksliniams skaičiavimo platformoms, kurios priklauso nuo sunkaus duomenų pralaidumo.

4. Pasirinktinė logika ir įterptasis pagreitis

Turėdama daugiau nei 60 000 loginių elementų ir turtingo laikrodžio valdymo, FPGA gali priglobti pritaikytus aparatūros greitintuvus konkrečiems algoritmams.Dizaineriai dažnai naudoja tai, kad būtų galima iškrauti skaičiavimo požiūriu intensyvias CPU užduotis, tokias kaip šifravimas, protokolo analizė ar realaus laiko valdymo kilpos.Tai taip pat gali integruoti kelis funkcinius blokus, todėl yra tinkamas sudėtingiems SOC panašiems dizainams.Šis lankstumas daro jį vertingą tokiose programose kaip pramoninė automatika, apsaugos sistemos ir aviacijos ir kosmoso valdymo blokai.

5. Prototipų kūrimo ir švietimo plėtros platformos

„EP2S60“ įrenginys dažniausiai randamas FPGA kūrimo rinkiniuose, naudojamuose prototipų kūrimui, testavimui ir akademiniams tyrimams.Jos loginės talpos balansas, I/O skaičius ir DSP galimybės leidžia inžinieriams ir studentams įgyvendinti ir patikrinti visas sistemas viename luste.Tai palaiko greitą skaitmeninių dizainų pakartojimą, leidžiantį patikrinti aparatinę įrangą prieš įsipareigojant plėtoti ASIC.Daugelis universitetų ir mokslinių tyrimų ir plėtros laboratorijų naudojasi tuo, kad mokytų pažangių skaitmeninių projektavimo ir signalų apdorojimo koncepcijų.

EP2S60F672C4 Panašios dalys

|

Specifikacija |

EP2S60F672C4 |

EP2S60F672C3N |

EP2S60F672C5 |

EP2S60F672C5N |

EP2S60F672I4

|

EP2S60F672I3N |

|

Šeima / serija |

„Stratix II“ |

„Stratix II“ |

„Stratix II“ |

„Stratix II“ |

„Stratix II“ |

„Stratix II“ |

|

Loginiai elementai (Le) |

60,440 |

60,440 |

60,440 |

60,440 |

60,440 |

60,440 |

|

Išmaldos |

24,176 |

24,176 |

24,176 |

24,176 |

24,176 |

24,176 |

|

Paketas |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

|

Greičio laipsnis |

C4 (STD) |

C3 (greičiau) |

C5 (greičiau) |

C5 (greičiau) |

I4 (std) |

I3 (greičiau) |

|

Temperatūros laipsnis |

Komercinė (0 ~ 70 ° C) |

Komercinė |

Komercinė |

Komercinė |

Pramoninė (−40 ~ 100 ° C) |

Pramoninė (−40 ~ 100 ° C) |

|

I/o kaiščiai |

492 |

492 |

492 |

492 |

492 |

492 |

|

Lusto atmintis |

2.4 Mbit |

2.4 Mbit |

2.4 Mbit |

2.4 Mbit |

2.4 Mbit |

2.4 Mbit |

|

Pagrindinė įtampa |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

|

Pagrindinis skirtumas |

Pradinis komercinis greitis |

C3 greičio šiukšliadėžė, be švino „N“ |

Didesnio greičio šiukšliadėžė |

Didesnio greičio šiukšliadėžė, „N“ variantas |

Pramoninė temperatūra, tas pats tankis |

Pramoninis, greitesnis greitis, be švino |

EP2S60F672C4 programavimo veiksmai

Prieš naudodami „EP2S60F672C4 FPGA“ savo dizaine, turite tinkamai sukonfigūruoti jį su savo sudarytu „Bitstream“.Šis procesas apima programavimo failo paruošimą, aparatūros sąsajos nustatymą ir užtikrinimą, kad konfigūracija teisingai įkeltų įjungimą.

1 žingsnis: sukurkite ir sudarykite savo dizainą

Pradėkite kurdami savo logikos dizainą naudodami „Intel Quartus II“ programinę įrangą.Baigę dizainą, jūs jį sudarote, kad sukurtumėte programavimo failą (.SOF arba .POF), specialiai EP2S60F672C4 įrenginiui.Kompiliacijos procesas patikrina laiko, kaiščio priskyrimo ir išteklių naudojimą, kad jūsų dizainas atitiktų FPGA architektūrą.Sudarę jūsų „Bitstream“ yra paruoštas įrenginio konfigūracijai.

2 žingsnis: nustatykite programavimo aparatinę įrangą

Tada jūs paruošite fizinio programavimo sąsają tarp savo kompiuterio ir FPGA plokštės.Paprastai tai apima USB-Blaster arba suderinamo JTAG laido sujungimą su įrenginio JTAG prievadu.Turėtumėte patikrinti, ar „Quartus II“ atpažįsta programuotoją ir kad tikslinis įrenginys yra teisingai aptinkamas.Šis žingsnis užtikrina stabilų ryšį prieš pradedant konfigūracijos procesą.

3 žingsnis: Įkelkite programavimo failą į įrenginį

Naudodami „Quartus II“ programuotojo įrankį, pridedate sudarytą .SOF arba .POF failą ir iš aptiktų įrenginių sąrašo pasirinkite EP2S60F672C4.Tada jūs inicijuojate programavimo seką, kurios metu bitų srautas perkeliamas ir įkeliamas į FPGA SRAM konfigūracijos ląsteles.Norėdami patvirtinti sėkmingą konfigūraciją, turėtumėte stebėti progreso juostą ir būsenos pranešimus.Baigęs FPGA nedelsdamas pradeda vykdyti užprogramuotą logiką.

4 žingsnis: patikrinkite konfigūraciją ir veikimą

Po programavimo jūs patikrinate, ar įrenginys veikia taip, kaip numatyta.„Quartus II“ pateikia patikrinimo parinktį, kaip patikrinti konfigūracijos CRC ir būsenos signalus, užtikrinant, kad dizainas būtų teisingai įkeltas.Taip pat galite išbandyti savo I/O funkcijas arba paleisti funkcinį modeliavimą, kad patvirtintumėte sistemos elgesį.Šis paskutinis žingsnis užtikrina, kad jūsų dizainas yra visiškai veikiantis ir stabilus ant aparatūros.

EP2S60F672C4 Privalumai ir trūkumai

Privalumai

• Didelis loginis tankis sudėtingiems dizainams

• Geras našumo ir sąnaudų santykis

• Lengva migracija toje pačioje šeimoje

• Stabilios ir brandžios plėtros įrankiai

• Įrodytas pramoninio naudojimo patikimumas

Trūkumai

• pasenęs ir sunkiau šaltinis

• Didesnė energijos suvartojimas nei naujesnės FPGA

• Nėra modernių greitųjų siųstuvų siųstuvų

• Sunkiau uždaryti laiką, kai jis bus naudojamas

• Ribotas būsimų protokolų mastelio keitimas

EP2S60F672C4 Pakuotės matmenys

|

Tipas |

Parametras |

|

Paketo tipas |

672-FBGA („Fineline BGA“) |

|

Kūno dydis (L × W) |

27,00 mm × 27,00 mm |

|

Bendras paketo aukštis (A) |

Maksimalus 3,50 mm |

|

STOCKOFF AUKŠTAS (A1) |

Min 0,30 mm |

|

Substrato storis (A2) |

Maksimalus 3,00 mm |

|

Rutulio skersmuo (B) |

0,50 mm - 0,70 mm |

|

Rutulio žingsnis (E) |

1,00 mm |

|

Rutulių skaičius |

672 |

|

Montavimo stilius |

Paviršiaus laikiklis |

|

Pakuotės aprašymas |

FBGA, 27 × 27 mm tinklelis |

EP2S60F672C4 Gamintojas

„EP2S60F672C4 FPGA“ yra pagamintas pagal „Altera Corporation“, pagrindinis programuojamų loginių prietaisų pradininkas.2015 m. Alterą įsigijo „Intel“, ir dabar produktas priklauso „Intel“ programuojamų sprendimų grupei (PSG), kuri ir toliau palaiko ir tiekia „Altera“ nustatytas FPGA šeimas.„Intel“ palaiko „Stratix II“ liniją kaip savo senojo produktų portfelio dalį, užtikrinant dokumentus, įrankių palaikymą ir ilgalaikį prieinamumą pramonės ir komunikacijos programoms.

Išvada

„EP2S60F672C4“ sujungia didelį loginio tankį, lanksčią atminties architektūrą ir tvirtas I/O funkcijas, kad palaikytų sudėtingas skaitmenines sistemas.Jo ALM pagrįstas dizainas, „Trimatrix ™“ atmintis, DSP blokai ir laikrodžio valdymo funkcijos leidžia efektyviai įgyvendinti reikalaujančias programas.Nors jis siūlo patikrintą patikimumą ir subrendusį vystymosi palaikymą, tačiau susiduria su tokiais apribojimais kaip pasenimas ir šiuolaikinių siųstuvų institucijų trūkumas, palyginti su naujesnėmis FPGA kartomis.Apskritai dėl subalansuoto našumo ir universalumo jis yra tvirtas pasirinkimas signalo apdorojimui, komunikacijai, duomenų tvarkymui ir prototipų nustatymui.

Duomenų lapas PDF

EP2S60F672C4 duomenų lapai:

Apie mus

ALLELCO LIMITED

Skaityti daugiau

Greitas užklausa

Prašau atsiųsti užklausą, mes nedelsdami atsakysime.

Dažnai užduodami klausimai [FAQ]

1. Ar EP2S60F672C4 gali veikti su šiuolaikinėmis DDR atminties sąsajomis?

Taip, jis palaiko DDR, DDR2, QDR II ir RLDRAM II sąsajas, kurios apima daugybę įprastų išorinės atminties standartų.Dėl to jis tinka aukšto lygio duomenų apdorojimo programoms.

2. Ar EP2S60F672C4 reikalauja specialaus tvarkymo ar saugojimo?

Taip, kaip ir kiti BGA supakuoti komponentai, jis turėtų būti laikomas drėgmės kontroliuojamoje pakuotėje ir tvarkoma su ESD apsauga.Tinkama laikymo praktika padeda išlaikyti litavimo ir įrenginio patikimumą surinkimo metu.

3. Kaip galite sumažinti energijos suvartojimą EP2S60F672C4 dizainuose?

Jei įmanoma, galite optimizuoti logikos panaudojimą, vartų nenaudojamus laikrodžius, mažesnę I/O įtampą ir pasinaudokite energijos sintezės parinktimis II kvartale, kad sumažintumėte bendrą galios brėžinį.

4. Kokie programavimo įrankiai reikalingi EP2S60F672C4?

Norėdami sukonfigūruoti įrenginį, jums reikės „Intel Quartus II“ programinės įrangos, skirtos projektuoti, kompiliuoti ir programuoti, kartu su USB-Blaster arba suderinamu JTAG kabeliu.

5. Ar EP2S60F672C4 palaiko lauko atnaujinimus ar nuotolinį pertvarkymą?

Taip, jis palaiko AES pagrįstą „BitsStream“ šifravimą ir nuotolinį pertvarkymą, leidžiantį saugiai atnaujinti sistemą, fiziškai nepakeičiant FPGA.

Viskas apie LFXP6C-3FN256C grotelių puslaidininkį

2025/10/6

XC2C256-7TQ144C CPLD: „Pinout“, funkcijos, programavimo ir duomenų lapų vadovas

2025/10/3

Populiarūs įrašai

-

Sudėtingos instrukcijos Nustatykite kompiuterius: kaip jie pakeitė skaičiavimą?

8000/04/18 147778

-

USB-C PINOUT ir funkcijos

2000/04/18 112035

-

„Xilinx Unified“ modeliavimo primityvų naudojimas: išsamus FPGA projektavimo ir modeliavimo vadovas

1600/04/18 111352

-

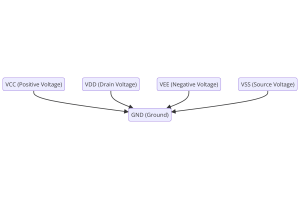

Maitinimo įtampa elektronikoje: VCC, VDD, VEE, VSS ir GND reikšmė

0400/04/18 83792

-

„RJ45“ jungties vadovas: „Pmout“, laidų, laidų tipai ir naudojimas

1970/01/1 79602

-

Pagrindinis vielos spalvų kodų vadovas šiuolaikinėse elektrinėse sistemose

Tai, kaip mūsų elektros sistemos naudoja spalvas, nėra tik išvaizdos.Kiekviena vielos spalva dabar rodo konkrečią funkciją, todėl montavimo ir priežiūros metu lengviau nustatyti ir tvarkyti elektro...1970/01/1 66976

-

Išvalymo vožtuvo vadovas: funkcija, simptomai, testavimas ir pakeitimas, kad būtų galima optimaliai atlikti variklio veikimą

Išvalymo vožtuvas yra pagrindinė automobilio sistemos dalis, padedanti išlaikyti orą švarų, valdant degalų garus, kol jie gali ištrūkti į atmosferą.Tai ne tik padeda aplinkai sumažinti taršą, bet i...1970/01/1 63111

-

Kokybės (Q) faktorius: lygtys ir programos

Kokybės koeficientas, arba „Q“, yra svarbus tikrinant, kaip gerai induktoriai ir rezonatoriai veikia elektroninėse sistemose, kuriose naudojami radijo dažniai (RF).„Q“ matuoja, kaip gerai grandinė ...1970/01/1 63044

-

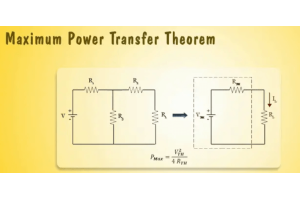

Pasiekti maksimalų našumą naudojant maksimalios galios perdavimo teoremą

Maksimalios galios perdavimo teorema paaiškina, kaip energija iš šaltinio, pavyzdžiui, akumuliatorius ar generatorius, teka į prijungtą apkrovą.Tai parodo tikslią sąlygą, kai apkrova gauna daugiaus...1970/01/1 54097

-

A23 akumuliatoriaus specifikacijos ir suderinamumas

„A23“ baterija yra maža, cilindro formos akumuliatorius, turintis aukštą įtampą.Taip pat vadinamas 23A, 23AE arba MN21, jis veikia esant 12 voltų ir daug aukštesnis nei AA ar AAA baterijos...1970/01/1 52198