EPM7064STC100-7 CPLD: funkcijos, programos ir sistemos programavimo vadovas

„EPM7064STC100-7“ yra galinga „Intel's Max® 7000S“ serijos lustas, skirtas tvarkyti sudėtingas užduotis elektroniniuose įrenginiuose.Šiame vadove aptariamos pagrindinės EPM7064STC100-7 ypatybės ir naudojimo būdai, pabrėždamas jo sugebėjimą lengvai perprogramuoti, greitą jo veikimą ir lanksčią dizainą.Idealiai tinka daugeliui skirtingų technologijų, pradedant mažomis programėlėmis ir baigiant didelėmis pramoninėmis mašinomis, ši lustas yra pagrindinis kūrinys, skirtas sukurti pažangias skaitmenines grandines.Katalogas

EPM7064STC100-7 Aprašymas

EPM7064STC100-7 yra sudėtingas programuojamas loginis įrenginys (CPLD) iš „Intel's Max® 7000s“ serijos.Jame yra 64 makrokaleliai ir 1250 vartų, kurie padeda sukurti sudėtingas skaitmenines grandines.Šis lustas veikia maksimaliu 166,7 MHz greičiu, o signalo uždelsimas yra 7,5 nanosekundės (NS).Jis turi 68 įvesties/išvesties (I/O) kaiščius, kurie veikia su 3,3 V ir 5 V logika, todėl jį lengva naudoti skirtingose grandinėse.Pagrindinė savybė yra jo 5,0 V sistemos programavimas (IPT) per JTAG sąsają (IEEE 1149.1).Tai reiškia, kad galite perprogramuoti jį neišimdami iš grandinės, palengvindami testavimą ir atnaujinimus.Jis yra 100 kontaktų plonos keturių plokščių pakuočių (TQFP), kuri yra kompaktiška, paviršiaus montuojama pakuotė.Šis CPLD naudojamas įterptosiose sistemose, skaitmeninio signalo apdorojimo, ryšių įrenginiuose ir pramonės automatizavimas.

Mes teikiame aukštos kokybės komponentus ir pritaikytas paslaugas, todėl geriausia pateikti savo masinį užsakymą su mumis patikimiems CPLD sprendimams.

EPM7064STC100-7 funkcijos

• Didelio tankio logika: „EPM7064STC100-7“ yra suprojektuotas su 64 makrokeliais ir 1250 tinkamų vartų, todėl jis yra labai tinkamas įgyvendinti sudėtingas logines funkcijas skaitmeninėse grandinėse.Ši didelio tankio architektūra leidžia sukurti sudėtingus loginius dizainus, išlaikant programuojamų loginių operacijų efektyvumą.Puikiai optimizuota makrofeldo struktūra užtikrina veiksmingą turimų išteklių panaudojimą, palaikant pažangų kombinuotą ir nuoseklųjį loginį diegimą.

• Greitas pasirodymas: Sukurtas greitųjų apdorojimui, EPM7064STC100-7 veikia maksimaliu vidiniu dažniu 166,7 MHz, leidžiant greitai vykdyti logines funkcijas.Jos sklidimo vėlavimas 7,5 ns užtikrina minimalų latenciją.Ši greito perjungimo galimybė padidina įrenginio galimybes efektyviai tvarkyti greitųjų duomenų apdorojimą, signalo kondicionavimą ir valdyti užduotis, todėl tai yra patikimas pasirinkimas reikalaujant skaitmeninių sistemų.

• Universalus I/O: Turėdamas 68 programuojamus įvesties/išvesties kaiščius, EPM7064STC100-7 siūlo išskirtinį lankstumą integracijai į įvairius grandinės dizainus.Palaikant tiek 3.3 V, tiek 5 V loginius lygius, jis leidžia sklandžiai suderinti su skirtinga sistemos įtampa, pašalinant poreikį papildomams įtampos lygio perjungikliams.Dėl šio pritaikomumo jis puikiai tinka pritaikyti mišrių įtampų aplinkoje, užtikrinant plačią pritaikomumą įterptųjų sistemų, pramonės kontrolės ir komunikacijos tinklus.

• Sistemos programavimas (IPT): Vienas iš „EPM7064STC100-7“ pranašumų yra jo 5,0 V sistemos programavimas (ISP), palengvintas per IEEE STD.1149.1 JTAG sąsaja.Ši funkcija leidžia perprogramuoti ir modifikuoti logines funkcijas, nenukreipiant ar fiziškai pašalinant įrenginį, supaprastinant techninę priežiūrą, derinimą ir iteracinį vystymąsi.IPT galimybė sumažina prastovą ir padidina programinės įrangos atnaujinimų lankstumą, todėl ji yra neįkainojama dinaminiams ir pertvarkomiems skaitmeniniams projektams.

EPM7064STC100-7 CAD modeliai

EPM7064STC100-7 simbolis

EPM7064STC100-7 pėdsakas

EPM7064STC100-7 3D modelis

EPM7064STC100-7 BLOCK DIAGRAM

EPM7064STC100-7 BLOCK DIAGRAM parodo, kaip lusto loginiai elementai yra sujungti ir valdomi.Jis turi keturis loginio masyvo blokus (laboratorijas), pažymėtus A, B, C ir D, kiekviename iš jų yra 16 makrokelinių.Šios makroelencijos atlieka logines funkcijas ir jungiasi per programuojamą sujungimo masyvą (PIA), leidžiančią lanksčią signalų nukreipimą.Kiekviena laboratorija yra susieta su I/O valdymo bloku, tvarkant iki 16 įvesties/išvesties kaiščių kiekvienoje laboratorijoje.Diagrama taip pat rodo globalius valdymo signalus (GCLK1, GCLK2, OE1 ir GCLRN), kurie padeda valdyti lusto laikiklio ir atkūrimo funkcijas.Kai kurie loginiai vartai apdoroja šiuos signalus prieš pasiekdami skirtingas sistemos dalis.EPM7064STC100-7 dizainas leidžia jį naudoti įvairiose programuojamose loginėse programose, tokiose kaip būsenos mašinos, adresų dekodavimas ir kitos pasirinktinės skaitmeninės grandinės.Jo lankstūs sujungimai užtikrina efektyvų signalo srautą ir patikimą veikimą.

EPM7064STC100-7 specifikacijos

|

Tipas |

Parametras |

|

Gamintojas |

Altera/intel |

|

Serija |

MAX® 7000S |

|

Pakuotė |

Dėklas |

|

Dalies būsena |

Pasenęs |

|

Programuojamas tipas |

Programuojamoje sistemoje |

|

Vėlavimo laikas TPD (1) MAX |

7,5 ns |

|

Įtampos tiekimas - vidinis |

4,75 V ~ 5,25 V. |

|

Loginių elementų/blokų skaičius |

4 |

|

Makrokelinių skaičius |

64 |

|

Vartų skaičius |

1250 |

|

I/O skaičius |

68 |

|

Darbinė temperatūra |

0 ° C ~ 70 ° C (TA) |

|

Montavimo tipas |

Paviršiaus laikiklis |

|

Paketas / atvejis |

100-TQFP |

|

Tiekėjo įrenginių paketas |

100-TQFP (14x14) |

|

Bazinis produkto numeris |

EPM7064 |

EPM7064STC100-7 Sistemos programavimo (ISP) seka

EPM7064STC100-7, „Max 7000S CPLD“ šeimos dalis, seka šešių pakopų sistemos programavimo (ISP) seka, kad užtikrintų teisingą konfigūraciją.Šis procesas leidžia jums užprogramuoti įrenginį, nenuimant jo iš plokštės.IPT procesas apima instrukcijų, adresų ir duomenų perkėlimą per TDI (bandymo duomenis) PIN kodą, tuo pačiu gaunant atsakymus per TDO (bandymo duomenis) PIN kodą.

Pirmasis etapas, Įveskite IPT, užtikrina, kad I/O kaiščiai sklandžiai pereis iš vartotojo režimo į IPT režimą ir reikalauja maždaug 1ms.Po to seka Patikrinkite ID, kur nuskaitytas įrenginio silicio ID, kad būtų patvirtintas teisingas taikinys.Toliau Birių ištrynimų Scenos poslinkiai ištrynimo instrukcijose ir taiko 100ms ištrinimo impulsą, išvalydamas visus esamus duomenis EEPROM ląstelėse. Programa Toliau seka etapas, kai adresai ir duomenys yra nuosekliai perkeliami į įrenginį, pritaikant programavimo impulsus, kad būtų sukonfigūruoti EEPROM langai.Kiekvienas adresas turi būti užprogramuotas atskirai, todėl šis žingsnis užima daug laiko, atsižvelgiant į EEPROM langelių skaičių įrenginyje.

Kai programavimas bus baigtas, Patikrinkite Etapas užtikrina, kad duomenys būtų saugomi teisingai.Čia skaitymo impulsai taikomi EEPROM ląstelėse, o gauti duomenys lyginami su numatomomis vertėmis.Jei nustatomi neatitikimai, gali prireikti perprogramuoti.Pagaliau Išėjimo IPT Stage užtikrinama, kad I/O kaiščiai pereitų prie vartotojo režimo, reikalaujant dar 1ms.Bendras programavimo ar patikrinimo laikas turi įtakos du pagrindiniai veiksniai: impulsų laikas, reikalingas EEPROM ištrinti, programavimui ir skaitymo operacijoms bei perjungimo laikas, kuris priklauso nuo TCK (bandymo laikrodžio) dažnio ir ciklų, reikalingų instrukcijų, adresų ir duomenų perdavimo perdavimo skaičiui.Kadangi skirtingi ISP galiojantys įrenginiai turi skirtingą EEPROM ląstelių skaičių, tiek bendras fiksuotas, tiek kintamas laikas yra išskirtinis kiekvienam įrenginiui.Bendrą IPT laiką galima apskaičiuoti kaip TCK dažnio funkciją, tikslinių įrenginių skaičių ir EEPROM architektūrą.

EPM7064STC100-7 programos

Įterptos sistemos

EPM7064STC100-7 yra plačiai naudojamas įterptosios sistemos programose, kur jis yra lankstus programuojamas loginis sprendimas įvairių periferinių įrenginių valdymui, apdorojimo signalams ir pritaikymo protokolams valdyti.Jos gebėjimas sąsajai su mikrovaldikliais ir jutikliais leidžia optimizuoti sistemos veikimą, išlaikant kompaktišką pėdsaką.Didelės spartos veikimas ir mažos energijos suvartojimas yra puikus pasirinkimas įterptoms programoms, kurioms reikalingas patikimumas ir efektyvumas.

Skaitmeninio signalo apdorojimas (DSP)

Skaitmeninio signalo apdorojime EPM7064STC100-7 vaidina vaidmenį įgyvendinant filtrus, signalo moduliaciją ir įvairias matematines funkcijas.Dėl greito perjungimo greičio ir mažo sklidimo uždelsimo jis tinka tvarkyti aukšto dažnio duomenų apdorojimo užduotis, užtikrinant minimalų signalo konvertavimo ir manipuliavimo vėlavimą.Jis dažniausiai naudojamas garso apdorojimo, telekomunikacijų ir radaro sistemose.

Duomenų ryšys

EPM7064STC100-7 yra plačiai naudojamas tinklų kūrimo ir duomenų ryšio sistemose dėl jo sugebėjimo tvarkyti intensyvias logikas, tokias kaip duomenų maršrutas, buferis ir klaidų taisymas.Jo programuojamos I/O galimybės leidžia jai prisitaikyti prie skirtingų ryšio protokolų, todėl tai yra vertingas komponentas Ethernet jungiklių, maršrutizatorių ir telekomunikacijų infrastruktūros.Jos palaikymas sistemos programavimui (IPT) taip pat įgalina lauko atnaujinimus, pagerindamas pritaikomumą dinaminėje tinklų kūrimo aplinkoje.

Pramoninė automatika

Pramoninės programos reikalauja didelio patikimumo, ilgaamžiškumo ir mažos energijos suvartojimo, todėl EPM7064STC100-7 yra pageidaujamas pasirinkimas programuojamiems logikos valdikliams (PLC), variklių valdymo sistemoms ir automatinei bandymo įrangai.Su JTAG pagrįstu programavimu sistemoje jis suteikia galimybę patobulinti automatizavimo procesus nereikalaujant fizinio pašalinimo ar pertvarkymo.Dėl universalumo įtampos suderinamume taip pat jis yra tinkamas sąsajoms su įvairiais jutikliais ir pavaromis, naudojamomis pramoninėje aplinkoje.

EPM7064STC100-7 Panašios dalys

EPM7064STC100-7 Privalumai

Sistemos programavimas (IPT)

Vienas didžiausių EPM7064STC100-7 pranašumų yra jo sugebėjimas būti perprogramuotas, kol jis vis dar montuojamas sistemoje.Tai pašalina poreikį pašalinti lustą atnaujinimams, sutrumpinti priežiūros laiką ir pagerinti efektyvumą.Galite įdiegti dizaino modifikacijas nenutraukdami gamybos, todėl tai yra ekonomiškai efektyvus sprendimas ilgalaikiams projektams.

Greitaeigis našumas

Įrenginys palaiko aukštą vidinį veikimo dažnį iki 166,7 MHz, leidžiantį greitai apdoroti duomenis ir reaguoti.Dėl to jis yra idealus programoms, reikalaujančioms signalo apdorojimo, logikos valdymo ir greitųjų sąsajų, užtikrinant sklandesnį ir patikimesnį sistemos veikimą.

Universalus I/O palaikymas

Turėdamas iki 68 konfigūruojamus I/O kaiščius ir suderinamumą su keliais įtampos lygiais (3,3 V, 5 V ir tolerantiškos 2,5 V, 3,3 V ir 5 V parinktys, EPM7064STC100-7 siūlo lankstumą projektuojant sistemą.Tai leidžia sklandžiai integruoti į įvairias grandines ir palaiko mišrios įtampos aplinką, sumažinant suderinamumo problemas su kitais komponentais.

Patikimas veikimas visoje aplinkoje

Sukurtas taip, kad veiktų nuo 0 ° C iki 70 ° C temperatūros diapazone, EPM7064STC100-7 užtikrina nuoseklų ir stabilų veikimą įvairiomis sąlygomis.Šis patikimumas daro jį tinkamesniu pasirinkimu programoms, kuriose reikalingas aplinkos stabilumas, pavyzdžiui, pramoninė automatizavimas, telekomunikacijos ir įterptosios valdymo sistemos.

EPM7064STC100-7 PAKETŲ PINIGO DIAGRAMA

„EPM7064STC100-7“ yra CPLD (sudėtingas programuojamas loginis įrenginys) iš „Altera's Max 7000S“ serijos, įsikūrusios 100 kontaktų ploname keturračio pakuotėje (TQFP-100).Šis paketo tipas yra skirtas pritvirtintame prie paviršiaus ir siūlo didelio kaiščių tankio ir kompaktiško dydžio balansą. PIN kodo diagrama Laikykitės numeravimo prieš laikrodžio rodyklę schemos, kai 1 kaištis yra viršutiniame kairiajame pakuotės kampe.Judant prieš laikrodžio rodyklę, pirmieji 25 kaiščiai užima kairę pusę, kaiščiai nuo 26 iki 50 yra išilgai apatinio krašto, kaiščiai nuo 51 iki 75 tęsiasi išilgai dešinės pusės, o kaiščiai nuo 76 iki 100 yra paskirstomi išilgai viršutinio krašto. TQFP-100 paketas Būtų ploni laidai, besitęsiantys į išorę iš visų keturių plokščio kvadratinio korpuso pusių.Ši konstrukcija padidina suderinamumą su paviršiumi ir išlaikant tinkamus kaiščio tarpus, kad būtų lengviau lietuoti ir surinkti.Švininis žingsnis (atstumas tarp gretimų kaiščių) paprastai yra 0,5 mm, optimizuodamas signalo vientisumą, tuo pačiu sumažinant bendrą pėdsaką.

EPM7064STC100-7 Gamintojas

EPM7064STC100-7 yra CPLD (sudėtingas programuojamas loginis įrenginys), kurį iš pradžių sukūrė puslaidininkių kompanija „Altera“, žinoma dėl programuojamų loginių sprendimų.2015 m., „Intel“ Įsigijo „Altera“, integruodama savo FPGA ir CPLD produktų linijas į „Intel“ programuojamų sprendimų grupę (PSG).Nuo to laiko EPM7064STC100-7 buvo pažymėtas „Intel“ prekės ženklu, nors jis buvo pažymėtas kaip pasenęs.„Intel“, kaip gamintojas, išlaikė seną „Max® 7000s“ serijos CPLD palaikymą, įskaitant šį modelį, palaipsniui perkeldamas dėmesį į šiuolaikines FPGA ir programuojamas logikos technologijas.

Išvada

„EPM7064STC100-7“ sujungia sudėtingas funkcijas, greitą našumą ir lengvus atnaujinimus viename luste, įrodant jo vertę sudėtingose skaitmeninėse sąrankose.Šis vadovas parodė, kaip jis veikia, kam jis naudojamas ir kaip jis tinka įvairioms elektroninėms sistemoms.Tai padeda padaryti įrenginius sklandžiai ir efektyviai, įrodant, kad tai vis dar labai naudinga daugeliui programų.Šis vadovas pateikia aiškų vaizdą, kaip EPM7064STC100-7 gali padėti efektyviai pagerinti elektroninius dizainus ir sistemos operacijas.

Duomenų lapas PDF

EPM7064STC100-7 duomenų lapai:

Apie mus

ALLELCO LIMITED

Skaityti daugiau

Greitas užklausa

Prašau atsiųsti užklausą, mes nedelsdami atsakysime.

Dažnai užduodami klausimai [FAQ]

1. Kaip „EPM7064STC100-7“ smūgio grandinės eksploatacinės savybės 7,5NS sklidimo uždelsimas?

7,5NS sklidimo uždelsimas užtikrina mažai latentinių signalų apdorojimą, todėl šis CPLD yra tinkamas greičiui tokioms greičiams kaip skaitmeninio signalo apdorojimas (DSP), ryšių sistemos ir pramoninė automatizavimas, kuriam reikalinga tiksli laiko valdymas.

2. Ar „EPM7064STC100-7“ galima užprogramuoti naudojant šiuolaikinius kūrimo įrankius?

Taip, tai galima užprogramuoti naudojant „Intel's Quartus II“ programinę įrangą (buvusią „Altera Quartus“) kartu su tinkamu JTAG programuotoju.Tačiau naujesnėse kvartavimo versijose gali būti ribota senesnių CPLDS, tokių kaip „EPM7064STC100-7“, gali būti ribota, todėl gali tekti naudoti senas versijas, tokias kaip „Quartus II 13.0 SP1“, kuri vis dar palaiko „MAX® 7000S“ serijos įrenginius.

3. Ar EPM7064STC100-7 palaiko mišrios įtampos aplinką?

Taip, jis palaiko ir 3.3 V, ir 5 V loginius lygius, todėl jis yra suderinamas su įvairiomis skaitmeninėmis grandinėmis.Šis lankstumas yra naudingas norint sujungti senus 5 V komponentus su šiuolaikinėmis 3.3v sistemomis be papildomos lygio keitimo grandinės.

4. Koks yra geriausias būdas pašalinti EPM7064STC100-7 pagrįstą dizainą?

Norėdami pašalinti triktis, galite naudoti „Quartus SignalTap II“ loginį analizatorių arba išorinius osciloskopus ir loginius analizatorius, kad stebėtumėte signalus.Jei „JTAG“ programavimo derinimas yra susijęs, įsitikinkite, kad TDI, TDO, TCK ir TMS jungtys yra teisingos ir kad jūs naudojate suderinamą USB sprogdintuvą arba „ByteBlasterMV“ programuotoją.

5. Ar galiu užprogramuoti EPM7064STC100-7, neišimdamas jo iš savo plokštės?

Taip.5,0 V sistemos programavimas (IPT) per JTAG (IEEE 1149.1) leidžia perprogramuoti įrenginį, kol jis lieka sistemoje.Tai leidžia atnaujinti programinę -aparatinę įrangą, derinti ir išbandyti daug efektyvesnius, palyginti su tradiciniais CPLD.

Išsamus 10K rezistoriaus vadovas: spalvų kodas, programos ir grandinės naudojimas

2025/03/10

Kondensatoriai ir baterijos: Kuris yra geriausias jūsų energijos poreikiams?

2025/03/7

Populiarūs įrašai

-

Sudėtingos instrukcijos Nustatykite kompiuterius: kaip jie pakeitė skaičiavimą?

8000/04/18 147778

-

USB-C PINOUT ir funkcijos

2000/04/18 112027

-

„Xilinx Unified“ modeliavimo primityvų naudojimas: išsamus FPGA projektavimo ir modeliavimo vadovas

1600/04/18 111351

-

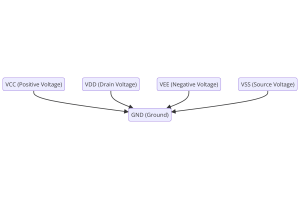

Maitinimo įtampa elektronikoje: VCC, VDD, VEE, VSS ir GND reikšmė

0400/04/18 83780

-

„RJ45“ jungties vadovas: „Pmout“, laidų, laidų tipai ir naudojimas

1970/01/1 79578

-

Pagrindinis vielos spalvų kodų vadovas šiuolaikinėse elektrinėse sistemose

Tai, kaip mūsų elektros sistemos naudoja spalvas, nėra tik išvaizdos.Kiekviena vielos spalva dabar rodo konkrečią funkciją, todėl montavimo ir priežiūros metu lengviau nustatyti ir tvarkyti elektro...1970/01/1 66971

-

Išvalymo vožtuvo vadovas: funkcija, simptomai, testavimas ir pakeitimas, kad būtų galima optimaliai atlikti variklio veikimą

Išvalymo vožtuvas yra pagrindinė automobilio sistemos dalis, padedanti išlaikyti orą švarų, valdant degalų garus, kol jie gali ištrūkti į atmosferą.Tai ne tik padeda aplinkai sumažinti taršą, bet i...1970/01/1 63107

-

Kokybės (Q) faktorius: lygtys ir programos

Kokybės koeficientas, arba „Q“, yra svarbus tikrinant, kaip gerai induktoriai ir rezonatoriai veikia elektroninėse sistemose, kuriose naudojami radijo dažniai (RF).„Q“ matuoja, kaip gerai grandinė ...1970/01/1 63041

-

Pasiekti maksimalų našumą naudojant maksimalios galios perdavimo teoremą

Maksimalios galios perdavimo teorema paaiškina, kaip energija iš šaltinio, pavyzdžiui, akumuliatorius ar generatorius, teka į prijungtą apkrovą.Tai parodo tikslią sąlygą, kai apkrova gauna daugiaus...1970/01/1 54097

-

A23 akumuliatoriaus specifikacijos ir suderinamumas

„A23“ baterija yra maža, cilindro formos akumuliatorius, turintis aukštą įtampą.Taip pat vadinamas 23A, 23AE arba MN21, jis veikia esant 12 voltų ir daug aukštesnis nei AA ar AAA baterijos...1970/01/1 52191