FPGA dizaino patobulinimas naudojant „Xilinx ISE“ įrankių vartotojo apribojimų failus (UCF)

Šis vadovas tiria vartotojo apribojimų failų (UCFS) vaidmenį tobulinant FPGA dizainą naudojant „Xilinx ISE“ įrankius.UCF leidžia pridėti konkrečius apribojimus, kad būtų geriau valdomas laikas, logika ir išdėstymas, o tai padidina projektavimo tikslumą, našumą ir patikimumą.Parodydamas, kaip efektyviai pritaikyti šiuos apribojimus, vadovas padeda supaprastinti projektavimo procesą, sumažinti derinimo laiką ir užtikrinti sėkmingą projekto pristatymą.Katalogas

UCFS tikslas ir vaidmuo FPGA dizaine

FPGA dizaine vartotojo apribojimų failai (UCFS) vaidina svarbų vaidmenį kontroliuojant, kaip jūsų kodo sintezuota logika yra fiziškai įdiegta luste.Šie failai leidžia nurodyti svarbius parametrus, tokius kaip laiko nustatymo apribojimai, kaiščių priskyrimai ir išsami informacija apie plotą, kurie gali tiesiogiai paveikti, ar dizainas atitinka našumo reikalavimus, ar ne.Pagalvokite apie UCFS kaip brėžinius, kurie užtikrina, kad viskas būtų teisingai išdėstyta, veikia pagal tvarkaraštį ir tvarkingai tinka vietoje.Suvaržymo nustatymo procesas prasideda ankstyvaisiais vystymosi etapais.Prieš sintezę pradėkite sukurti UCF failą, užtikrindami, kad parametrai būtų užrakinti nuo pat pradžių.Po sintezės sugeneruojami papildomi apribojimų failai, tokie kaip „NetList“ suvaržymo failas (NCF) ir fizinio apribojimo failas (PCF), kad atspindėtų logikos pakeitimus ir baigtų fizinius apribojimus.Kiekvienas iš šių failų remiasi ankstesniu žingsniu, palaipsniui tobulinant dizainą.UCF yra teksto failai, parašyti ASCII formatu, tai reiškia, kad juos galima redaguoti naudojant pagrindinius teksto redaktorius arba daugiau specializuotų įrankių, tokių kaip „Xilinx“ apribojimų redaktorius.Dėl šio paprastumo UCF yra labai prieinami ir lankstūs pasinerti į apribojimų nustatymų specifiką, nereikia per daug sudėtingų įrankių.

Kaip apribojimai formuoja FPGA dizainą?

FPGA dizaine suvaržymai vaidina svarbų vaidmenį formuojant, kaip lustas veikia, ir sąveikauja su išoriniais įrenginiais.Šie apribojimai yra apibrėžti UCF (vartotojo apribojimų faile), kuris veikia kaip išsamus projektavimo įrankio instrukcijų rinkinys, nurodant, kaip FPGA vidiniai komponentai turėtų būti sujungti ir valdyti.Pagrindiniai apribojimai apima laiko nustatymo apribojimus, kurie užtikrina signalų keliones tarp komponentų per tam tikrą laiką, kad būtų išlaikytas patikimas našumas norimu laikrodžio greičiu.Kaiščių priskyrimų žemėlapis Fiziniai FPGA kaiščiai prie išorinių įrenginių, tokių kaip jutikliai, atminties moduliai ar ryšių sąsajos, užtikrinant tikslius ryšius.Plotijos apribojimai kontroliuoja loginių lusto loginių blokų išdėstymą, kad būtų išvengta spūsčių, sumažintų vėlavimus ir optimizuotų išteklių naudojimą.Be šių apribojimų automatizuotos priemonės priims sprendimus dėl išdėstymo ir maršruto, tačiau dažnai su neoptimaliais rezultatais, dėl kurių laiko nustatymo problemos, kliūtys ar neefektyvūs lustų išdėstymai.Naudodamiesi UCF failais, daugelis išlaiko šių kritinių aspektų valdymą, todėl FPGA dizainas geresnis našumas, efektyvumas ir patikimumas.

Iteracinis suvaržymo tobulinimo pobūdis

FPGA dizainas retai yra vieno ir atlikto procesas.Kai dizainas vystosi ir kyla naujų iššūkių, keičiami apribojimai ir keičiasi per visą kūrimo ciklą.Kiti koreguoja UCF failus, kad atitiktų našumo tikslus, išspręstų laiko nustatymo problemas ar prisitaikytų prie kintančių projekto reikalavimų.Šis pakartotinis tobulinimas yra svarbi FPGA darbo eigos dalis.Pvz., Jei pastebite, kad signalo kelias užtrunka per ilgai, kad būtų sklisti tarp dviejų komponentų, jie gali modifikuoti UCF, kad pakeistų laiko apribojimą arba perkeltų tuos komponentus, kad sumažintų vėlavimą.Panašiai, jei PIN paskirstymas prieštarauja išorinei aparatinei įrangai, UCF gali būti redaguojama, kad būtų išspręstas neatitikimas.Kiekviena UCF peržiūra perkelia dizainą arčiau norimo rezultato, kiekvienas koregavimas moko daugiau apie kompromisus, susijusius su FPGA optimizavimu.Šis testavimo, koregavimo ir mokymosi ciklas ne tik pagerina dizainą, bet ir paaštrina įgūdžius.

UCF naudojimo pranašumai

Taikant apribojimus naudojant UCF failus, yra keletas praktinių pranašumų, kurie prisideda prie FPGA projektų sėkmės:

• Patobulintas laiko tikslumas: Gerai pagaminti laiko apribojimai užtikrina, kad FPGA patikimai veiktų norimo laikrodžio greičiu, išvengiant klaidų, kurias sukelia signalo vėlavimas.

• Geresnis išteklių panaudojimas: ploto apribojimai neleidžia loginių blokų dėti per arti vienas kito ar per toli vienas nuo kito, optimizuodami lusto erdvę ir pagerinti našumą.

• Supaprastintas derinimas: kontroliuodami kaiščių priskyrimą ir signalo nukreipimą, UCF padeda sumažinti maršruto nustatymo konfliktus, todėl bandymo metu bus lengviau diagnozuoti ir išspręsti problemas.

Apie mus

ALLELCO LIMITED

Skaityti daugiau

Greitas užklausa

Prašau atsiųsti užklausą, mes nedelsdami atsakysime.

Konkrečios programos standartiniai produktai (ASSPS): naujovių skatinimas šiuolaikinėje elektronikoje

2025/01/8

Programuojamo lusto (SOPC) sistema: technologija, dizainas ir programos

2025/01/8

Populiarūs įrašai

-

Sudėtingos instrukcijos Nustatykite kompiuterius: kaip jie pakeitė skaičiavimą?

8000/04/18 147758

-

USB-C PINOUT ir funkcijos

2000/04/18 111960

-

„Xilinx Unified“ modeliavimo primityvų naudojimas: išsamus FPGA projektavimo ir modeliavimo vadovas

1600/04/18 111349

-

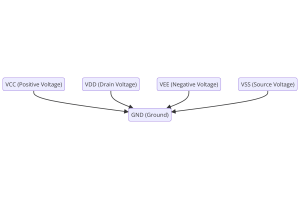

Maitinimo įtampa elektronikoje: VCC, VDD, VEE, VSS ir GND reikšmė

0400/04/18 83726

-

„RJ45“ jungties vadovas: „Pmout“, laidų, laidų tipai ir naudojimas

1970/01/1 79511

-

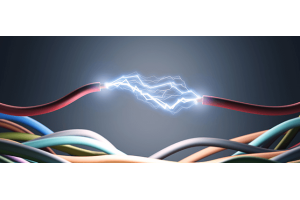

Pagrindinis vielos spalvų kodų vadovas šiuolaikinėse elektrinėse sistemose

Tai, kaip mūsų elektros sistemos naudoja spalvas, nėra tik išvaizdos.Kiekviena vielos spalva dabar rodo konkrečią funkciją, todėl montavimo ir priežiūros metu lengviau nustatyti ir tvarkyti elektro...1970/01/1 66929

-

Išvalymo vožtuvo vadovas: funkcija, simptomai, testavimas ir pakeitimas, kad būtų galima optimaliai atlikti variklio veikimą

Išvalymo vožtuvas yra pagrindinė automobilio sistemos dalis, padedanti išlaikyti orą švarų, valdant degalų garus, kol jie gali ištrūkti į atmosferą.Tai ne tik padeda aplinkai sumažinti taršą, bet i...1970/01/1 63078

-

Kokybės (Q) faktorius: lygtys ir programos

Kokybės koeficientas, arba „Q“, yra svarbus tikrinant, kaip gerai induktoriai ir rezonatoriai veikia elektroninėse sistemose, kuriose naudojami radijo dažniai (RF).„Q“ matuoja, kaip gerai grandinė ...1970/01/1 63019

-

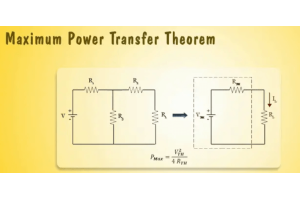

Pasiekti maksimalų našumą naudojant maksimalios galios perdavimo teoremą

Maksimalios galios perdavimo teorema paaiškina, kaip energija iš šaltinio, pavyzdžiui, akumuliatorius ar generatorius, teka į prijungtą apkrovą.Tai parodo tikslią sąlygą, kai apkrova gauna daugiaus...1970/01/1 54086

-

A23 akumuliatoriaus specifikacijos ir suderinamumas

„A23“ baterija yra maža, cilindro formos akumuliatorius, turintis aukštą įtampą.Taip pat vadinamas 23A, 23AE arba MN21, jis veikia esant 12 voltų ir daug aukštesnis nei AA ar AAA baterijos...1970/01/1 52156