LVPECL paaiškino: Žemos įtampos teigiamo emiterio sujungtos logikos vadovas

Žemos įtampos teigiamos emiterio sujungta logika (LVPECL) yra pagrindinė skaitmeninės logikos technologijos pažanga, pritaikyta patenkinti žemos įtampos aplinkos reikalavimus.Veikia esant 3,3 V arba 2,5 V, „LVPECL“ vystosi iš tradicinės teigiamos emitatorių sujungtos logikos (PECL), kuri priklauso nuo 5,0 V maitinimo šaltinio.Šis poslinkis pabrėžia didėjantį energiją taupančių sprendimų pabrėžimą, kuris susilieja su dideliu našumu su sumažėjusia energijos suvartojimu.Pagrindinis istorinėje emitterio sujungtos logikos (ECL) plėtroje, LVPECL suteikia aiškių pranašumų didelės spartos programose, įskaitant telekomunikacijas ir skaičiavimą, kai energijos vartojimo efektyvumas ir signalo vientisumas yra rimtas.Šis straipsnis įsigilina į LVPECL savybes, privalumus ir projektavimo aspektus, paaiškindamas jo transformacinį vaidmenį šiuolaikinėje elektronikoje.Nuo praktinių pritaikymų iki techninių skirtumų sužinokite, kaip LVPECL formuoja skaitmeninių sistemų ateitį.

Katalogas

ECL klasifikacija

|

Tipas |

VCC |

Vee |

|

PECL |

5,0 v |

0,0 V. |

|

LVPECL |

3.3 V. |

0,0 V. |

|

2,5VPECL |

2.5 v |

0,0 V. |

|

2.5vnecl |

0,0 V. |

-2,5 v |

|

Lvnecl |

0,0 V. |

-3.3 v |

|

Necl |

0,0 V. |

-5,0 v |

ECL/PECL/LVPECL logikos privalumai

• ECL logika išsiskiria dėl nepaprastai mažos išėjimo varžos, paprastai krinta nuo 6 iki 8 omų.Ši savybė yra sujungta su išskirtinai didele įvesties varža, kuri gali būti laikoma beveik begaline.Tokios charakteristikos įgalina ECL įspūdingas vairavimo galimybes, leidžiančias jai valdyti perdavimo linijas, kurių būdingi varžos svyruoja nuo 50 iki 130 omų, reikšmingai nesumažėjus kintamos kintamos veiklos.Gebėjimas palaikyti signalo vientisumą dideliais atstumais dažniausiai yra aktyvi tokiose programose kaip plokštumos laidai ir dideli kabelių važiavimai, kur dominuoja signalo kokybės išsaugojimas.

• ECL prietaisų atsparumas įtampos ir temperatūros svyravimams yra dar vienas pastebimas bruožas, išskiriantis juos iš TTL ir CMOS technologijų.Šis stabilumas pasirodo naudingas aplinkoje, kuriai būdingos skirtingos sąlygos, užtikrinant nuoseklų našumą.Be to, ECL laikrodžių tvarkyklių pagaminti laikrodžiai pasižymi didesne sinchronizavimu ir sumažinta iškrypėliu, kurie yra naudingi perduodant spartus duomenis.Laiko tikslumas prisideda prie sustiprinto bendrojo sistemos veikimo, daugiausia programų, reikalaujančių griežtų laiko apribojimų.

• Palyginus ECL su kitais signalizacijos metodais, atsiranda aiškus skirtumas dėl dažnio palaikymo.ECL gali gerai valdyti dažnius, viršijančius 10 GHz, tuo tarpu LVD paprastai uždengia maždaug 1,5 GHz.Ši galimybė ECL apibūdina kaip nepaprastą greičio programų pasirinkimą, o eksploatavimo greitis viršija 5 GHz ir vėluoja nuolat išlaikyti 1N.Dėl tokios veikimo metrikos ECL ypač naudinga mažoms ir vidutinėms integruotoms grandinėms ir ypač didelėms greičiams skaitmeninėms sistemoms, kur svarbu kiekviena nanosekundė.

• ECL suderinamumas su platesniu perdavimo linijos varžų spektru yra pastebimas pranašumas.Skirtingai nuo LVD, kuriam reikalingas specifinis 100-osios oso nutraukimo rezistorius, kad būtų palaikomas signalo vientisumas, ECL pritaikymas prie skirtingų varžų sumažina signalo atspindžio tikimybę ir susijusias komplikacijas.Šis lankstumas ne tik supaprastina projektavimo aspektus, bet ir sustiprina įvairių programų patikimumą.Gebėjimas efektyviai funkcionuoti įvairiose varžybose įgalina jus integruoti ECL į platesnę sistemų įvairovę be griežtų reikalavimų, paprastai susijusių su kitomis technologijomis.

ECL/PECL/LVPECL logikos trūkumai

Nors „Emitter Couped Logic“ (ECL) gali pasigirti įspūdingais pranašumais greitaeigių sričių srityje, tačiau jis taip pat turi pastebimų trūkumų, į kuriuos reikia atkreipti dėmesį.Pagrindinės problemos apima padidėjusį energijos suvartojimą, ribotą triukšmo toleranciją ir pažeidžiamumą išoriniams trukdžiams.ECL grandinių loginis svyravimas yra tik 0,8 V, suporuotas su DC triukšmo tolerancija tik 200 mv.Ši savybė pabrėžia kompromisą, kai ECL išskirtinės greičio galimybės atsiranda dėl energijos efektyvumo ir atsparumo dėl triukšmo trikdžių.Realiuose scenarijuose tai gali sukelti iššūkių, ypač aplinkoje, kur energijos suvartojimas yra rizikingas arba kai signalo vientisumas yra nepaprastai svarbus.

Teigiamo emiterio sujungtos logikos (PECL) standartinė išėjimo apkrova nustatoma 50 omų su VCC-2V tiekimo įtampa.Remiantis šiais parametrais, tipiški statiniai Out+ ir OUT-OUT yra VCC-1,3 V, o išvesties srovė yra 14 mA.Nors ši konfigūracija pasirodo veiksminga tam tikroms programoms, ji gali gerai nesutapti su visomis situacijomis, ypač atsižvelgiant į šiluminio valdymo sudėtingumą ir su šiais išvesties lygiais susijusių galios išsklaidymo padariniais.

PECL išėjimo grandinės struktūra

PECL įvestis yra diferencialinė pora, turinti didelę įvesties varžą.Norint pasiekti maksimalų dinaminio įvesties signalo lygį, šios diferencialinės poros bendro režimo įtampa turi būti šališka iki VCC - 1,3 V.Kai kuriuose lustuose yra integruota šališkumo grandinė, leidžianti tiesiogiai susisiekti be papildomų komponentų.Tačiau lustai be šios įmontuotos šališkumo grandinės naudojimo metu turi būti taikomas išorinis nuolatinės srovės paklaida.

PECL įvesties grandinės struktūra

PECL loginio lygio standartas

|

Parametras |

Sąlyga |

Min |

Tipiškas |

Maks |

Vienetas |

|

Išėjimo aukšta |

Ta = 0 ° C ~ 85 ° C |

VCC - 1,025 |

- |

VCC - 0,88 |

V |

|

TA = 40 ° C. |

VCC - 1,085 |

- |

VCC - 0,88 |

V |

|

|

Išėjimo žemas |

Ta = 0 ° C ~ 85 ° C |

VCC - 1,81 |

- |

VCC - 1,62 |

V |

|

TA = 40 ° C. |

VCC - 1,83 |

- |

VCC - 1,55 |

V |

|

|

Įvestis aukšta |

- |

VCC - 1,16 |

- |

VCC - 0,88 |

V |

|

Įvestis žemas |

- |

VCC - 1,81 |

- |

VCC - 1,48 |

V |

Apie mus

ALLELCO LIMITED

Skaityti daugiau

Greitas užklausa

Prašau atsiųsti užklausą, mes nedelsdami atsakysime.

4N25 OPTOCOUBLER: SAVYBĖS, PINOUTAS IR LENKIOS

2024/12/27

D882 Tranzistorius paaiškino: „Pinout“, konfigūracija ir saugaus naudojimo patarimai

2024/12/27

Populiarūs įrašai

-

Sudėtingos instrukcijos Nustatykite kompiuterius: kaip jie pakeitė skaičiavimą?

8000/04/18 147778

-

USB-C PINOUT ir funkcijos

2000/04/18 112029

-

„Xilinx Unified“ modeliavimo primityvų naudojimas: išsamus FPGA projektavimo ir modeliavimo vadovas

1600/04/18 111351

-

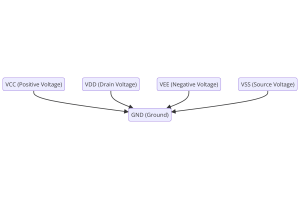

Maitinimo įtampa elektronikoje: VCC, VDD, VEE, VSS ir GND reikšmė

0400/04/18 83782

-

„RJ45“ jungties vadovas: „Pmout“, laidų, laidų tipai ir naudojimas

1970/01/1 79579

-

Pagrindinis vielos spalvų kodų vadovas šiuolaikinėse elektrinėse sistemose

Tai, kaip mūsų elektros sistemos naudoja spalvas, nėra tik išvaizdos.Kiekviena vielos spalva dabar rodo konkrečią funkciją, todėl montavimo ir priežiūros metu lengviau nustatyti ir tvarkyti elektro...1970/01/1 66972

-

Išvalymo vožtuvo vadovas: funkcija, simptomai, testavimas ir pakeitimas, kad būtų galima optimaliai atlikti variklio veikimą

Išvalymo vožtuvas yra pagrindinė automobilio sistemos dalis, padedanti išlaikyti orą švarų, valdant degalų garus, kol jie gali ištrūkti į atmosferą.Tai ne tik padeda aplinkai sumažinti taršą, bet i...1970/01/1 63107

-

Kokybės (Q) faktorius: lygtys ir programos

Kokybės koeficientas, arba „Q“, yra svarbus tikrinant, kaip gerai induktoriai ir rezonatoriai veikia elektroninėse sistemose, kuriose naudojami radijo dažniai (RF).„Q“ matuoja, kaip gerai grandinė ...1970/01/1 63041

-

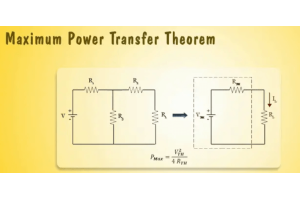

Pasiekti maksimalų našumą naudojant maksimalios galios perdavimo teoremą

Maksimalios galios perdavimo teorema paaiškina, kaip energija iš šaltinio, pavyzdžiui, akumuliatorius ar generatorius, teka į prijungtą apkrovą.Tai parodo tikslią sąlygą, kai apkrova gauna daugiaus...1970/01/1 54097

-

A23 akumuliatoriaus specifikacijos ir suderinamumas

„A23“ baterija yra maža, cilindro formos akumuliatorius, turintis aukštą įtampą.Taip pat vadinamas 23A, 23AE arba MN21, jis veikia esant 12 voltų ir daug aukštesnis nei AA ar AAA baterijos...1970/01/1 52193