Signalo apdorojimo AD9959 funkcijų supratimas

AD9959 yra galingas ir lankstus skaitmeninis sintezatorius, siūlantis keturių nepriklausomų kanalų dažnio, fazės ir amplitudės kontrolę.Šis straipsnis apima pagrindines AD9959 funkcijas, technines specifikacijas ir įprastas programas, todėl jums lengviau suprasti, kaip šis įrenginys gali būti naudojamas įvairiose sąrankose.Nesvarbu, ar norite sukurti judrus vietinius osciliatorius, ar sinchronizuoti sudėtingas sistemas, tokias kaip fazių masyvo radarai, AD9959 suteikia tikslumą ir pritaikomumą, reikalingą įvairiems projektams.Iki šio vadovo pabaigos turėsite aiškiai suprasti, kaip veikia AD9959 ir kaip jis gali būti pritaikytas skirtingose srityse.Katalogas

AD9959 apžvalga

AD9959 Siūlo keturis tiesioginius skaitmeninio sintezatoriaus šerdes, leidžiančias savarankiškai valdyti dažnį, fazę ir amplitudę kiekvienam kanalui.Turėdamas galimybę valdyti iki 16 moduliacijos lygių, nesvarbu, ar tai dažnis, fazė ar amplitudė, jis suteikia lankstumo jūsų dizainui.Kadangi visi kanalai turi tą patį sistemos laikrodį, jie išlieka sinchronizuojami, užtikrindami sklandų veikimą keliuose kanaluose.Be to, jei dirbate su daugiau nei vienu AD9959, galite lengvai sinchronizuoti kelis įrenginius, todėl tai idealiai tinka sudėtingoms sąrankoms.

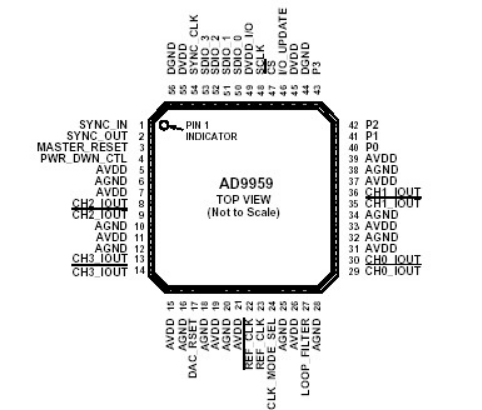

AD9959 PINOUT diagrama

| Nr. | Mnemoninis | I/o | Aprašymas |

| 1 | SYNC_IN | I | Naudojamas keliems AD9959 įrenginiams sinchronizuoti.Jungiasi prie pagrindinio AD9959 įrenginio „Sync_out“ kaiščio. |

| 2 | SYNC_OUT | O | Naudojamas keliems AD9959 įrenginiams sinchronizuoti.Jungiasi su vergo AD9959 „Sync_in“ kaiščiu. |

| 3 | Master_reset | I | Aktyvus aukšto nustatymo kaištis.Patvirtindamas „Master_reset“ kaištį, AD9959 vidinius registrus verčia į savo numatytąją būseną. |

| 4 | Pwr_dwn_ctl | I | Išorinis valdymas įjungimą. |

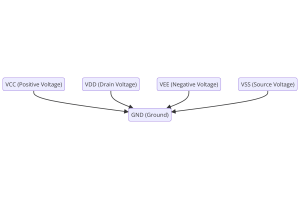

| 5, 7, 11, 15, 19, 21, 26, 31, 33, 37, 39 | Avdd | I | Analoginio maitinimo kaiščiai (1,8 V). |

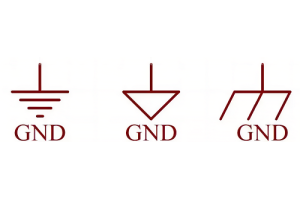

| 6, 10, 12, 16, 18, 20, 25, 28, 32, 34, 38 | Agnd | I | Analoginiai žemės kaiščiai. |

| 44, 56 | DVDD | I | Skaitmeniniai maitinimo šaltinio kaiščiai (1,8 V). |

| 45, 55 | DGND | I | Skaitmeninės galios žemės smeigtukai. |

| 8 | CH2_IOUT | O | Tikroji DAC išvestis.Baigiasi AVDD. |

| 9 | CH2_IOUT | O | Papildomas DAC išėjimas.Baigiasi AVDD. |

| 13 | CH3_IOUT | O | Tikroji DAC išvestis.Baigiasi AVDD. |

| 14 | CH3_IOUT | O | Papildomas DAC išėjimas.Baigiasi AVDD. |

| 17 | DAC_RSET | I | Nustato visų DAC atskaitos srovę.1,91 kΩ rezistorius (nominalus) yra prijungtas nuo 17 kaiščio iki AGND. |

| 22 | Ref_clk | I | Papildomas etaloninis laikrodžio/osciliatoriaus įvestis.Kai „Ref_Clk“ valdomas vieno tipo režimu, šis PIN kodas turėtų būti atsiejamas iki AVDD arba AGND su 0,1 µF kondensatoriumi. |

| 23 | Ref_clk | I | Nuorodos laikrodžio/osciliatoriaus įvestis.Kai „Ref_Clk“ valdomas vieno tipo režimu, tai yra įvestis.Norėdami pamatyti etaloninį laikrodžio konfigūraciją, skaitykite skyrių „Operacija“. |

| Nr. | Mnemoninis | I/o | Aprašymas |

| 24 | Clk_mode_sel | I | Valdymo kaištis osciliatoriaus skyriui.ATSARGIAI: Neišvairuokite šio kaiščio už 1,8 V.Kai aukštas (1,8 V), osciliatoriaus skyrius įgalinamas priimti kristalą kaip REF_CLK šaltinį.Kai žemas osciliatoriaus skyrius apeina. |

| 27 | „Loop_filter“ | I | Jungiasi prie PLL kilpos filtro išorinio nulio kompensavimo tinklo.Paprastai tinklą sudaro 0Ω rezistorius iš eilės su 680pf kondensatoriumi, susietu su AVDD. |

| 29 | CH0_IOUT | O | Papildomas DAC išėjimas.Baigiasi AVDD. |

| 30 | CH0_IOUT | O | Tikroji DAC išvestis.Baigiasi AVDD. |

| 35 | CH1_IOUT | O | Papildomas DAC išėjimas.Baigiasi AVDD. |

| 36 | CH1_IOUT | O | Tikroji DAC išvestis.Baigiasi AVDD. |

| 40–43 | P0 iki P3 | I | Duomenų kaiščiai, naudojami moduliacijai (FSK, PSK, AQUE), paleisti/sustabdyti šluotos akumuliatorius arba naudojami padidinti/padidinti išvesties amplitudę.Duomenys yra sinchroniški su „Sync_Clk“ (54 kaištis).Duomenų įvestys turi atitikti „Sync_Clk“ sąrankos ir laiko reikalavimus.Šių kaiščių funkcionalumą valdo profilio kaiščio konfigūracijos (PPC) bitai (FR1 [14:12]). |

| 46 | I/O_UPDATE | I | Kylantis kraštas perduoda duomenis iš nuoseklaus I/O prievado buferio į aktyvius registrus.I/O_UPDATE yra sinchroninis su „Sync_Clk“ (54 kaištis).I/O_UPDATE turi atitikti „Sync_clk“ sąrankos ir laiko reikalavimus, kad garantuotų fiksuoto vamzdyno duomenų vėlavimą į DAC išvestį;Priešingu atveju egzistuoja ± 1 sync_clk vamzdyno neapibrėžtumo laikotarpis.Mažiausias impulsų plotis yra vienas sinchronizavimo laikotarpis. |

| 47 | CS \ | I | Aktyvus žemo lusto pasirinkimas.Leidžia keliems įrenginiams bendrinti bendrą I/O magistralę (SPI). |

| 48 | SCLK | I | Serijos duomenų laikrodis I/O operacijoms.Duomenų bitai užrašomi ant kylančio SCLK krašto ir perskaitykite ant krintančio SCLK krašto. |

| 49 | DVDD_I/O. | I | 3.3V Skaitmeninis maitinimo šaltinis SPI prievadui ir skaitmeniniam I/O. |

| 50 | SDIO_0 | I/o | Duomenų PIN SDIO_0 yra skirtas tik serijinio prievado I/O. |

| 51, 52 | SDIO_1, SDIO_2 | I/o | Duomenų kaištis SDIO_1 ir duomenų kaištis SDIO_2 gali būti naudojami serijiniam I/O prievadui arba naudojami DAC išvesties amplitudės rampos/rampos (RU/RD) inicijavimui. |

| 53 | SDIO_3 | I/o | Duomenų kaištis SDIO_3 gali būti naudojamas serijiniam I/O prievadui arba DAC išvesties amplitudės padidinimui/didmiesčiui (RU/RD).Vieno arba 2 bitų režimais SDIO_3 naudojamas sinchronizuoti/o.Jei funkcija „Sync_i/O“ nenaudojama, pririškite ją prie žemės ar logikos 0. Neleiskite SDIO_3 plūduriuoti vienkartiniais arba 2 bitų režimais. |

| 54 | SYNC_CLK | O | „Sync_Clk“ veikia ketvirtadalis sistemos laikrodžio greičio;Tai galima išjungti.I/O_UPDATE arba DUOMENYS (40 kaištis - 43 kaištis) yra sinchroninis iki sinchronizavimo_clk.Norėdami garantuoti fiksuoto vamzdyno duomenų vėlavimą į DAC išvestį, I/O_UPDATE arba DUOMENYS (40 kaištis - 43 kaištis) turi atitikti sąrankos ir laiko reikalavimus kylančiam sync_clk kraštui;Priešingu atveju įvyksta ± 1 sinchronizavimo laikotarpis. |

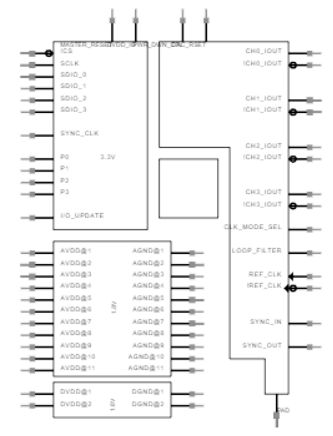

AD9959 CAD modelio apžvalga

AD9959 simbolis

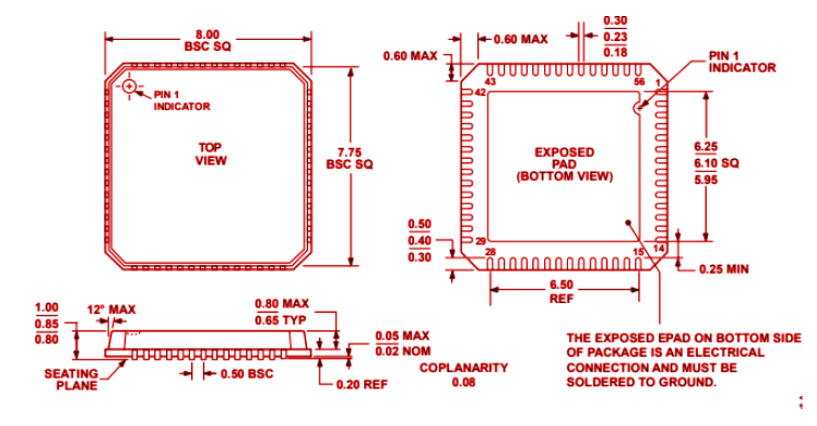

AD9959 pėdsakas

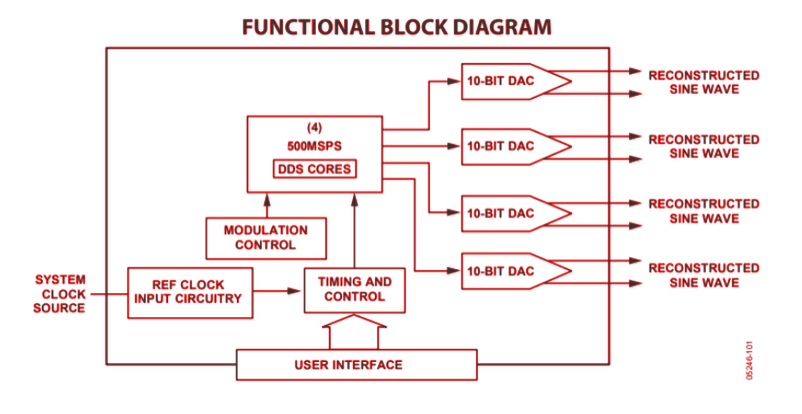

Išsami AD9959 bloko diagrama

AD9959 Techninės specifikacijos

Techninės specifikacijos, atributai, parametrai ir palyginamos „Analog Devices Inc.“ AD9959BCPZ dalys.

| Tipas | Parametras |

| Gyvenimo ciklo būsena | |

| Gamyklos švino laikas | 8 savaitės |

| Kreipkitės į dengimą | Alavas |

| Kalno | Paviršiaus laikiklis |

| Montavimo tipas | Paviršiaus laikiklis |

| Paketas / atvejis | 56-VFQFN eksponuotas padas, CSP |

| Smeigtukų skaičius | 56 |

| Darbinė temperatūra | -40 ° C iki 85 ° C. |

| Pakuotė | Dėklas |

| JESD-609 kodas | E3 |

| PBFREE kodas | Ne |

| Dalies būsena | Aktyvus |

| Jautrumo drėgmės lygis (MSL) | 3 (168 valandos) |

| Terminacijų skaičius | 56 |

| Nutraukimas | SMD/SMT |

| ECCN kodas | Ear99 |

| Papildoma funkcija | Taip pat reikia 3,3 V tiekimo |

| Maksimali galios išsklaidymas | 680MW |

| Įtampa - tiekimas | 1,71 V - 1,96 V. |

| Terminalo padėtis | Keturratis |

| Terminalo forma | Nėra švino |

| Didžiausia reflovos temperatūra (° C) | 260 |

| Tiekimo įtampa | 1,8 V. |

| Terminalo žingsnis | 0,5 mm |

| Dažnis | 500MHz |

| Laikas @ smailės reflow temp (-os) | 30 |

| Bazinės dalies numeris | AD9959 |

| PIN kodas | 56 |

| Kvalifikacijos būsena | Ne kvalifikuotas |

| Darbinė tiekimo įtampa | 1,8 V. |

| Sąsaja | Serija |

| Veikimo tiekimo srovė | 180Ma |

| Nominali tiekimo srovė | 160Ma |

| Maksimalus tiekimo srovė | 185MA |

| UPS/UCS/Periferinio ICS tipas | |

| Bitų skaičius | 10 |

| Mėginių ėmimo greitis | 500 MSP |

| Ribinis nuskaitymas | Ne |

| Mažos galios režimas | Taip |

| Konversijos kursas | 500 MSP |

| D/A keitiklių skaičius | 4 |

| Skiriamoji geba (bitai) | 10 b |

| Žodžio plotis (bitai) | 32 b |

| Ūgis | 830 μm |

| Ilgis | 8 mm |

| Plotis | 8 mm |

| Pasiekti SVHC | Nėra SVHC |

| ROHS būsena | ROHS3 suderinamas |

| LENGVAS NEMOKAMAS | Yra švino |

AD9959 pagrindinės savybės

4 sinchronizuoti DDS kanalai esant 500 MSP

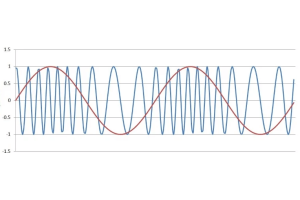

AD9959 teikia keturis sinchronizuotus tiesioginio skaitmeninio sintezatoriaus (DDS) kanalus, kurie visi veikia iki 500 MSP.Tai leidžia generuoti tikslus signalus keliuose kanaluose, išlaikant sinchronizaciją, o tai ypač naudinga dirbant su projektais, kuriems reikalingi keli rezultatai, veikiantys sklandžiai.

Nepriklausomas dažnis, fazė ir amplitudės valdymas

Kiekvienas iš keturių DDS kanalų siūlo nepriklausomą dažnio, fazės ir amplitudės kontrolę.Tai leidžia tiksliai sureguliuoti kiekvieną kanalą, kad atitiktų skirtingus poreikius, suteikiant lankstumo tvarkant įvairius signalo parametrus.

Dažnio, fazės ir amplitudės pokyčių suderintos latencijos

AD9959 užtikrina, kad dažnio, fazės ir amplitudės pokyčiai yra sinchronizuojami visuose kanaluose.Tai reiškia, kad koreguojant vieną parametrą, pakeitimas vyksta tuo pačiu metu visuose kanaluose, padėdami išlaikyti nuoseklius išėjimus be atsilikimo.

Puiki kanalo izoliacija

Turėdamas daugiau nei 65 dB kanalo ir kanalo izoliaciją, AD9959 sumažina trukdžius tarp kanalų.Tai užtikrina, kad kiekviename kanale sugeneruoti signalai yra švarūs ir ryškūs, suteikdami aukštesnės kokybės jūsų dizaino našumą.

Linijinė valymo galimybė

AD9959 palaiko linijinį dažnį, fazę ir amplitudės valymą.Ši funkcija leidžia sklandžiai pereiti tarp verčių, todėl lengviau generuoti signalus, kurie palaipsniui keičiasi laikui bėgant, o tai gali būti naudinga bandymo ir kalibravimo tikslams.

Iki 16 dažnio, fazių ir amplitudės moduliacijos lygių

Įrenginys gali valdyti iki 16 moduliacijos lygių dažniui, fazei ar amplitudei.Šis lankstumo lygis leidžia įgyvendinti įvairias moduliavimo schemas, pradedant nuo paprasto iki sudėtingo, atsižvelgiant į jūsų projekto poreikius.

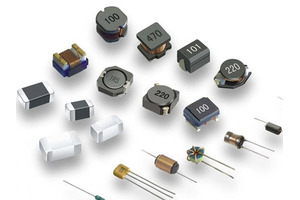

Integruoti 10 bitų skaitmeniniai ir analoginiai keitikliai (DAC)

Kiekvienas kanalas turi savo integruotą 10 bitų DAC, leidžiantį tiksliai paversti skaitmeninius signalus į analoginius išėjimus.Tai daro AD9959 puikiu pasirinkimu, kai jums reikia tikslios analoginio signalo generavimo kompaktiška forma.

Individualiai programuojamos DAC viso masto srovės

Galite užprogramuoti kiekvieno DAC viso masto srovę atskirai, o tai leidžia valdyti kiekvieno kanalo išvesties galią.Šis pritaikymo lygis leidžia optimizuoti skirtingų kanalų galios lygį, atsižvelgiant į jūsų specifinius reikalavimus.

Smulkaus dažnio derinimo skiriamoji geba

AD9959 siūlo 0,12 Hz ar geresnės derinimo skiriamąją gebą, užtikrinančią tikslią jūsų generuojamų signalų dažnio kontrolę.Šis tikslumo lygis yra naudingas dirbant su programomis, kai mažos dažnio pakeitimai daro didelę įtaką.

Aukštos skiriamosios gebos fazės poslinkis

Turėdamas 14 bitų fazių poslinkio skiriamąją gebą, AD9959 leidžia tiksliai sureguliuoti kiekvieno kanalo fazę.Ši funkcija yra naudinga, kai jums reikia tikslių fazių koregavimų tarp signalų, pavyzdžiui, suderinant kelis signalus fazinėse matrico sistemose.

Išėjimo amplitudės mastelio keitimas

AD9959 teikia 10 bitų išėjimo amplitudės mastelio skiriamąją gebą.Tai leidžia labai tiksliai sureguliuoti išvesties amplitudę, suteikiančią lankstumą, kad signalo stiprumą būtų galima tiksliau valdyti.

Patobulinta serijos I/O prievado sąsaja

Serijos I/O prievado sąsaja (SPI) siūlo padidėjusį duomenų pralaidumą, leidžiantį greitai ir efektyviai perduoti duomenis tarp įrenginio ir jūsų sistemos.Tai pagreitina ryšį, kuris gali būti naudingas greito tempo programose.

Valdymas išjungti

AD9959 apima ir programinę įrangą, ir aparatinės įrangos parinktis, leidžiančias išjungti, kad galėtumėte valdyti, kaip ir kada išsaugoti energiją.Ši savybė yra ypač naudinga kuriant energiją sąmoningus dizainus, kai prioritetas yra energijos efektyvumas.

Dvigubo tiekimo operacija

Įrenginys veikia su dviguba tiekimo sistema: 1,8 V DDS šerdyje ir 3,3 V serijiniam I/O.Ši konfigūracija padeda subalansuoti našumą atsižvelgiant į galios poreikius, todėl ji yra pritaikoma įvairioms projektavimo aplinkai.

Keli prietaisų sinchronizavimas

AD9959 palaiko sinchronizaciją keliuose įrenginiuose, leidžiant išplėsti savo dizainą papildomais vienetais, išlaikant tikslų laiko nustatymą.Tai leidžia lengviau išplėsti savo projektus neprarandant sinchronizacijos.

Pasirenkamas „Refclk“ daugiklis

Kai pasirenkamas „Refclk“ daugiklis svyruoja nuo 4 × iki 20 ×, AD9959 siūlo lankstumą laikydamiesi pasirinkimo variantų, leidžiančių pasirinkti geriausią jūsų dizaino nustatymą.

Integruotas „Refclk Crystal Oscillator“

Įrenginyje yra įmontuotas „Refclk Crystal Oscillator“, kuris supaprastina jūsų projektavimo procesą, sumažinant išorinių komponentų poreikį, todėl lengviau valdyti laiką sistemoje.

Kompaktiškas 56 švino LFCSP paketas

AD9959 yra 56 švino LFCSP pakete, suteikiančioje kompaktišką ir erdvę taupymo parinktį, kaip integruoti kelis DDS kanalus į jūsų dizainą.Šis mažos formos faktorius yra idealus, kai jums reikia aukšto funkcionalumo, nesiimant per daug vietos lentos.

Bendros AD9959 programos

Agile vietiniai generatoriai

AD9959 yra tinkamai pritaikytas naudoti judriuose vietiniuose generatoriuose, užtikrinant tikslią dažnio, fazės ir amplitudės kontrolę.Tai daro jį puikiu pasirinkimu, kai jums reikia lanksčios ir reguliuojamos signalo generavimo radijo sistemose ar kitoje ryšių įrangoje.

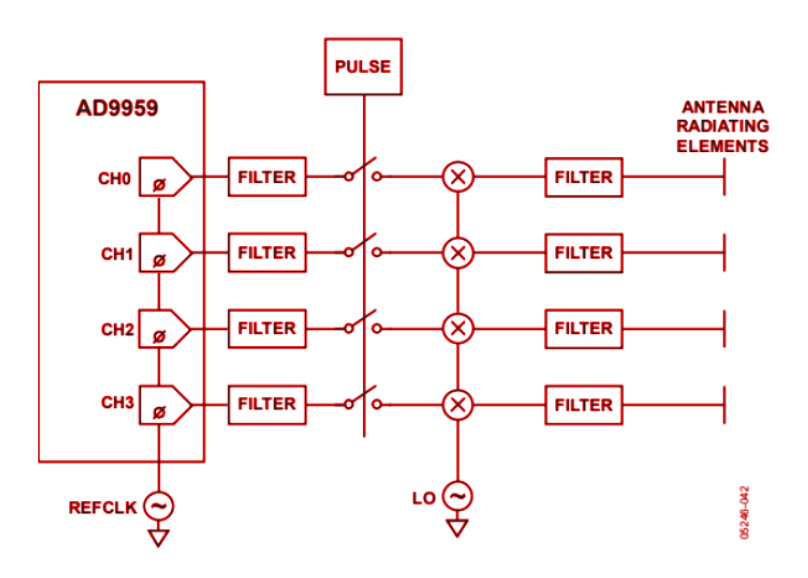

Fazių masyvo radarai ir sonarai

Faziniame masyvo radaro ir sonaro sistemose labai svarbu tiksliai sinchronizuoti kelis signalo kanalus.AD9959 sugebėjimas tvarkyti nepriklausomą valdymą ir sinchronizaciją keliuose kanaluose daro jį puikiai tinkantį šioms programoms, užtikrinant tikslų signalo apdorojimą ir laiką.

Instrumentai

AD9959 gali būti naudojamas įvairių tipų prietaisuose, ypač įrenginiuose, kuriems reikalingas tikslus signalo generavimas ir valdymas.Nesvarbu, ar tai skirta bandymams, matavimui ar kalibravimui, įrenginio lankstumas reguliuojant dažnį, fazę ir amplitudę padidina jūsų dizaino universalumą.

Sinchronizuotas laikymasis

Projektams, kuriems reikalingas sinchronizuotas laikymasis keliuose kanaluose, AD9959 siūlo puikų sprendimą.Jo įmontuotos sinchronizacijos funkcijos leidžia išlaikyti tikslų laiką tarp kanalų, todėl jis yra idealus sistemoms, kuriose laiko tikslumas yra labai svarbus.

RF šaltinis, skirtas akusto-optiniam derinamųjų filtrų (AOTF)

AD9959 gali veikti kaip RF šaltinis, skirtas akusto-optiniam derinamųjų filtrų (AOTF), užtikrinant patikimą ir tikslų signalo generavimą šioms optinėms sistemoms.Jo lankstumas dažnio ir amplitudės valdymo metu leidžia patenkinti tokių specializuotų programų reikalavimus.

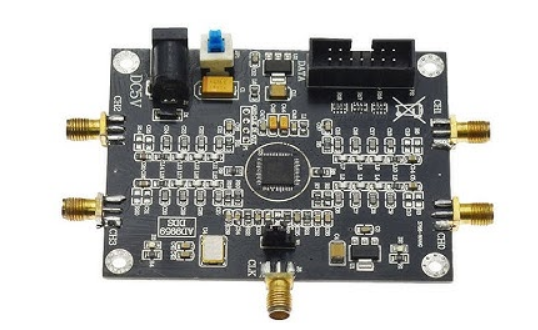

AD9959 Taikymo grandinės apžvalga

AD9959 matmenų kontūro diagrama

AD9959 Gamintojo informacija

„Analog Devices“ yra pagrindinė įmonė kuriant integruotas grandines nuo 1965 m. Bendrovė specializuojasi kurdama ir kuriant grandines, kurios padeda konvertuoti, būklę ir proceso signalus iš realaus pasaulio, pavyzdžiui, temperatūros, garso ir judesio - elektros signalų.Šios grandinės naudojamos įvairiose elektroninėse sistemose visame pasaulyje.

Dažnai užduodami klausimai [DUK]

1. Kam naudojamas AD9959?

AD9959 yra keturios tiesioginės skaitmeninio sintezatoriaus (DDS) šerdys, kiekviena iš jų leidžia nepriklausomai kontroliuoti savo kanalą dažnį, fazę ir amplitudę.Šis lankstumas gali padėti subalansuoti bet kokius signalų neatitikimus, kuriuos sukelia analoginiai procesai, tokie kaip filtravimas, amplifikacija ar išdėstymo skirtumai PCB.

2. Kaip veikia AD9959?

AD9959 gali modifikuoti dažnį, fazę ar amplitudę (naudojant FSK, PSK arba paprašykite moduliacijos), kurio lygis yra iki 16.Jūs kontroliuojate šią moduliaciją, pritaikydami signalus profilio kaiščiams, o tai leidžia lustui perjungti skirtingus moduliacijos lygius pagal poreikį.

Apie mus

ALLELCO LIMITED

Skaityti daugiau

Greitas užklausa

Prašau atsiųsti užklausą, mes nedelsdami atsakysime.

Išsamus TC7660COA įtampos keitiklio vadovas

2024/10/24

„Tip120“ tranzistoriaus supratimas

2024/10/24

Populiarūs įrašai

-

Kas yra GND grandinėje?

1970/01/1 2924

-

RJ-45 jungties vadovas: RJ-45 jungties spalvų kodai, laidų schemos, R-J45 programos, RJ-45 duomenų lapai

1970/01/1 2484

-

Pluošto jungčių tipai: SC vs LC ir LC VS MTP

1970/01/1 2075

-

Suprasti maitinimo įtampą elektronikoje VCC, VDD, VEE, VSS ir GND

0400/11/8 1863

-

Palyginimas tarp DB9 ir Rs232

1970/01/1 1756

-

Kas yra LR44 baterija?

Elektra, ši visur esanti jėga, tyliai persmelkia kiekvieną mūsų kasdienio gyvenimo aspektą, pradedant nuo nereikšmingų įtaisų iki gyvybei pavojingos medicinos įrangos, ji vaidina tylų vaidmenį.Tačiau tikrai suvokti šią energiją, ypač tai, kaip ją laikyti ir efektyviai išvesti, nėra lengva užduotis.Šiame straipsnyje pagrindinis dėmesys bus skiriamas monetų elementų baterij...1970/01/1 1706

-

Supratimas apie pagrindus: atsparumas induktyvumui, ir operatyvumas

Sudėtingame elektros inžinerijos šokyje pagrindinių elementų trijulė užima svarbiausią vietą: induktyvumas, pasipriešinimas ir talpa.Kiekvienas turi unikalius bruožus, kurie diktuoja dinaminius elektroninių grandinių ritmus.Čia mes pradedame kelionę iššifruoti šių komponentų sudėtingumą, atskleisti jų skirtingus vaidmenis ir praktinius naudojimo būdus didžiuliame elektrini...1970/01/1 1649

-

„CR2430“ akumuliatoriaus išsamus vadovas: specifikacijos, programos ir palyginimas su CR2032 baterijomis

Kas yra CR2430 akumuliatorius?CR2430 baterijų pranašumaiNormaCR2430 akumuliatoriaus pritaikymasCR2430 ekvivalentasCR2430 VS CR2032Baterija CR2430 dydisKo ieškoti perkant CR2430 ir ekvivalentusDuomenų lapas PDFDažnai užduodami klausimai Baterijos yra mažų elektroninių prietaisų širdis.Tarp daugelio turimų tipų monetų ląstelės vaidina lemiamą vaidmenį, dažniausiai randamą skaiči...1970/01/1 1536

-

Kas yra RF ir kodėl mes jį naudojame?

Radijo dažnio (RF) technologija yra pagrindinė šiuolaikinio belaidžio ryšio dalis, leidžianti perduoti duomenis dideliais atstumais be fizinių jungčių.Šis straipsnis gilinasi į RF pagrindus, paaiškindamas, kaip elektromagnetinė radiacija (EMR) leidžia RF ryšiui.Mes ištirsime EMR principus, RF signalų kūrimą ir valdymą bei jų plačią naudojimą.Straipsnyje taip pat aprašomi i...1970/01/1 1528

-

CR2450 VS CR2032: Ar vietoj to galima naudoti akumuliatorių?

Ličio mangano baterijos turi tam tikrų panašumų su kitomis ličio baterijomis.Didelis energijos tankis ir ilgas tarnavimo laikas yra bendros savybės.Dėl tokios baterijos laimėjo daugelio vartotojų pasitikėjimą ir palankumą dėl savo unikalios saugos.Brangios technologijos įtaisai?Maži prietaisai mūsų namuose?Apsidairykite ir pamatysite juos visur.Tarp šių daugelio ličio-Manganese...1970/01/1 1497