„D flip-Flops“ supratimas: darbas, programos ir pranašumai

Šis vadovas paaiškina, kas yra D flip-flop ir kaip jis veikia skaitmeninėse grandinėse.Taip pat sužinosite apie 4 ir 8 bitų skląsčius, kaip jie veikia kartu ir kur jie naudojami.Vadove yra pavyzdžiai, kaip D flip-flops naudojami kompiuteriuose, laikmačiuose, ryšių sistemose ir įterptame įrenginiuose.Čia taip pat pasakojama apie geras ir blogas puses, kai jūsų dizainas naudoja „D flip-Flops“.Katalogas

Kas yra D flip-flop?

A D Flip-Flop (Trumpai tariant, „duomenys“ arba „delsos“ „Flip-Flop“) yra pagrindinis skaitmeninės elektronikos elementas, naudojamas vienam dvejetainei informacijai saugoti.Jis veikia tiksliai su laiku, fiksuodama ir palaikant duomenis tik tada, kai laikrodžio signalas paprastai keičiasi kylančiame ar krintančiame krašte, atsižvelgiant į dizainą.Kai ateina laikrodžio kraštas, D (duomenų) įvestis esanti vertė perkeliama į išvestį, pažymėta Q. Po to išvestis išlieka fiksuota, net jei duomenų įvestis keičiasi iki kito galiojančio laikrodžio krašto.

2 paveikslas. D flip flop blokinė schema

Yra du pagrindiniai veikimo būdai: sinchroniniai ir asinchroniniai.Į Sinchroninis režimas, „D Flip-Flop“ reaguoja tik į laikrodžių signalus, užtikrindamas visas grandinės keitimo būsenos dalis.Į asinchroninis režimas, papildomi įvestys, tokios kaip „Preset“ ar „Clear“, gali nepaisyti išvesties būsenos nelaukdami laikrodžio, leisdami greitai inicijuoti ar iš naujo nustatyti.Standartinis D flip-flop turi du įvestis: duomenys (d) ir laikrodis (CLK).Aktyvaus laikrodžio krašto metu jis fiksuoja įvesties vertę.Kai laikrodis neaktyvus, išėjimas stabilus.

Kaip veikia D flip-flop?

D flip-flop, paprastai žinomas kaip „duomenys“ arba „delsos“ flip-flop, funkcionuoja sinchronizuodami su laikrodžio signalu.Pagrindinis jo mechanizmas yra paprastas: jis ima įvesties vertę (D) esant tam tikram laikrodžio perėjimui (paprastai kylančiam kraštui) ir perduoda tą vertę į išvestį (q).Papildomas išėjimas (Q ′) turi atvirkštinį Q., nes jis reaguoja tik laikrodžio krašte, „D flip-flop“ yra patikimas saugojimo elementas skaitmeninėse grandinėse.

3 paveikslas. D flip-flop loginė grandinė

Viduje „D Flip-Flops“ dažnai kuriami naudojant loginių vartų konfigūraciją pagrindiniame vergo ar vartų užrakto sąrankoje.Pateiktoje diagramoje pavaizduotas NAND vartų pagrindu pagamintas Dvinas, kuris veikia panašiai.Pagrindiniai įėjimai yra D (duomenys) ir CLK (laikrodis), o išėjimai yra q ir q ′.Kai CLK yra žemas, grandinė ignoruoja D pokyčius, palaikydama srovės išėjimą.Kai CLK pakyla aukštai, grandinė atnaujina: jei D yra aukštas, q tampa aukštas, o q ′ tampa žemas;Jei D yra žemas, q tampa žemas, o q ′ tampa aukštas.Kai laikrodis grįžta į žemą, išėjimas užfiksuojamas, išsaugantis jo būseną iki kito laikrodžio impulsų.

Tiesos lentelė padeda išsiaiškinti tokį elgesį.Kai laikrodis neaktyvus ar pereinamas, Q ir Q ′ laikosi stabiliai.Kylančiame laikrodžio krašte Q paima dabartinę d vertę (1, jei d yra aukštas, 0, jei d yra žemas), o Q ′ tampa jos atvirkštine.Šis krašto sukeltas atsakymas užtikrina, kad laikrodžio krašte yra tik duomenys, todėl „Flip-Flop“ yra stabilus ir atsparaus triukšmo ar greito įvesties pokyčiams tarp laikrodžio ciklų.

D Flip-Flop Tiesos lentelė

|

CLK |

D |

Q (kita būsena) |

Q ' |

|

0 (žemas) |

X |

Q (nepakitęs) |

Q ' |

|

↑ (kylantis kraštas) |

0 |

0 |

1 |

|

↑ (kylantis kraštas) |

1 |

1 |

0 |

|

1 (aukštas, be krašto) |

X |

Q (nepakitęs) |

Q ' |

Ši lentelė iliustruoja, kad „D flip-flop“ atnaujina savo išvestį tik ant kylančio laikrodžio signalo krašto, kuris yra, kai laikrodis pereina iš žemos į aukštą.Bet kuriuo kitu metu jis išlaiko ankstesnį išvestį, nepaisydamas visų duomenų įvesties pakeitimų.Dėl šio nuspėjamo, krašto jautrus elgesys daro D flip-flop vertingą skaitmeninėse sistemose, kur reikia tikslaus laiko ir sekos kontrolės.

Duomenų užraktų naudojimas „D flip-Flops“

Be jų vaidmens kontroliuojant laiko valdymą, „D flip-Flops“ taip pat veikia kaip duomenų užraktai.Duomenų užraktas tam tikru metu turi įvesties vertę ir palaiko ją stabilią, kol to prireiks.Tai naudinga norint atskirti vieną grandinės dalį nuo kito arba išsaugoti duomenis apdorojimo metu.Užraktas veikia pagal laikrodį arba įjungimo signalą.Kai aktyvus, jis perduoda įvestį į išvestį.Kai neaktyvus, jis užfiksuoja esamą išėjimą vietoje, nepaisant tolesnių įvesties pakeitimų.

Įrenginiai, tokie kaip 74LS74 (TTL) ir 4042 (CMOS), yra integruotų grandinių, kuriuose yra keli D flip-flops, pavyzdžiai.Šiuos įrenginius galima sugrupuoti kuriant atminties registrus ar valdymo blokus.Kai keli flip-flops sukelia tas pats valdymo signalas, jie gali saugoti kelių bitų duomenų vertes, veikdami kaip laikina skaitmeninės informacijos laikymo vieta.

4 bitų duomenų skląstis

4 paveikslas. 4 bitų duomenų užraktas

Diagramoje parodytą 4 bitų duomenų skląsčiui sudaro keturi D tipo Flip-Flops (pažymėti FFA į FFD), kiekvienas atsakingas už vieno bitų dvejetainio įvesties kaupimą.Šie flip-flopai yra lygiagrečiai lygiagrečiai ir lemia bendras laikrodžio signalas, užtikrinant, kad visi keturi užfiksuotų atitinkamas įvesties vertes vienu metu ant laikrodžio krašto.

Kiekvienas „Flip-Flop“ gauna atskirą įvesties bitą (A, B, C ir D) ir išveda saugomą vertę per savo Q išėjimą.Kai aktyvus laikrodžio impulsas, dabartinės įvesties vertės yra užfiksuotos į Flip-flops.Užfiksavę šios vertės išlieka stabilios ir prieinamos išvestyje, kol ateis kitas laikrodžio impulsas, veiksmingai laikant arba „užrakinant“ duomenis.

Ši struktūra leidžia skląsčiui tarnauti kaip kompaktiškas 4 bitų registras arba laikinas duomenų saugojimo įrenginys.Tai vertinga skaitmeninėse sistemose, kurioms reikalingas sinchronizuotas duomenų perdavimas, pavyzdžiui, aritmetiniai loginiai vienetai, instrukcijų vamzdynai ar adresų magistralės.Fiksuodamas duomenis apie bendrą laikrodžio signalą, skląstis užtikrina tikslią kontrolę, kai duomenys saugomi ir perkeliami į grandinę.

Skaidrus duomenų skląstis

Skirtingai nuo „Edge“ sukeltų Flip-Flops, skaidrus skląstis nuolat perduoda įvesties duomenis į išvestį tol, kol jo įgalinimo signalas yra aktyvus.Dėl tokio elgesio jis idealiai tinka programoms, kai duomenų srautas reikalingas, kol komanda užšals dabartinę išvestį.

74LS373 yra tipiškas skaidrus skląstis.Kai jo įgalinimo signalas yra didelis, duomenys iš įvesties į išvestį teka laiku.Kai įjungimo signalas sumažėja, dabartiniai išėjimai yra užrakinti, o tai neturi įtakos įvesties pokyčiams.

Tokio tipo skląstis dažnai apima „Tri-State“ išėjimus, kurie gali atjungti nuo bendros magistralės, kai to nereikia.Tai apsaugo nuo signalo konfliktų ir leidžia keliems įrenginiams naudoti tas pačias duomenų linijas be trikdžių.Skaidrūs užraktai yra įprasti atminties prieigos grandinėse, demultipleksavimo logikai ir sistemoms, kurioms reikalingas laikinas, bet patikimas duomenų fiksavimas.

8 bitų duomenų skląstis

5 paveikslas. 8 bitų duomenų užraktas

Aukščiau pavaizduotas 8 bitų duomenų skląstis remiasi mažesnių skląsčių principais, įtraukiant aštuonis lygiagrečius D flip-flops, galinčius saugoti visą baitą duomenis nuo D0 iki D7.Ši sąranka dažniausiai matoma integruotose grandinėse, tokiose kaip 74LS373.Visi aštuoni Flip-Flops yra sugrupuoti į skląsčio bloką, kuris fiksuoja įvesties duomenis ant kylančio bendrojo laikrodžio (CLK) signalo kylančio krašto.Kai laikrodis yra aktyvus ir patvirtinama įjungimo (EN) eilutė, dabartinės įvesties vertės yra užfiksuotos ir pateikiamos išėjimo.

Prijungta prie skląsčio yra trijų būsenų išvesties etapas.Ši funkcija leidžia išėjimams (nuo Q0 iki Q7) arba įvesti duomenų linijas arba įvesti aukštos varžos (HI-Z) būseną, atsižvelgiant į išvesties įgalinimo (OE) valdymą.Šis trijų būsenų elgesys yra svarbus sistemoms, apimančioms bendrus duomenų magistrales, nes tai neleidžia signalo susidūrimams, kai keli įrenginiai gali pasiekti tas pačias linijas.Tokie 8 bitų skląsčiai yra puikūs skaitmeninėse sistemose sinchronizavimui ir laikinai saugoti baitų masto duomenis.Jie dažnai randami mikroprocesorinėse sąsajose, atminties adresų fiksavime ir I/O įrenginiuose, kur jie veikia kaip tarpininkai tarp greitų duomenų šaltinių ir lėtesnių ar sinchroninių sistemos komponentų.

„D flip-Flops“ programos

D Flip-Flops yra labai svarbūs daugelyje skaitmeninių sistemų.Jie padeda tinkamai sekti laiką ir saugoti duomenis, o tai yra naudinga tokiems dalykams, kaip tvarkyti įvykius, užtikrindami, kad signalai yra susieti, ir trumpam laikomi duomenys.Nuo kompiuterio lustų iki įrenginių, kurie siunčia ir gauna duomenis, „D Flip-Flops“ yra pagrindinė šiuolaikinės elektronikos veikimo dalis.

D „Flip-Flop“ duomenų saugojimui

6 paveikslas. D duomenų saugojimo Flip-flop

Paveikslėlyje parodyta lygiagrečiai sujungtų D flip-flops grupė, kiekviena iš jų saugo po truputį duomenų (D0 iki D3).Kartu jie sudaro 4 bitų registrą.Visi „Flip-Flops“ turi tą patį laikrodžio signalą (CLK), taigi, kai atsiranda laikrodžio impulsas, visi įėjimai saugomi tuo pačiu metu ir siunčiami į išėjimus (Q0 iki Q3).Tokie registrai yra naudojami ALUS saugoti rezultatus, I/O sistemose, kad būtų galima laikyti duomenis pervedimų metu, ir valdymo blokuose, kad būtų galima sekti instrukcijas.Kadangi „Flip-Flops“ yra suaktyvinami, jie tiksliai saugo duomenis kiekviename laikrodžio krašte, o tai padeda tiksliai nustatyti laiką.Nors tokio tipo saugykla yra laikina (duomenys prarandami, kai galia išjungta), ji yra labai greita, todėl ji yra naudinga buferiams ir trumpalaikei atminčiai.

D Flip-Flops duomenų perdavimui

7 paveikslas. D duomenų perdavimo flippai

Paveikslėlyje pavaizduoti D flip-flops, sujungti grandinėje, kad būtų sudarytas poslinkio registras.Duomenys patenka į vieną kartą per nuosekliųjų duomenų įvestį ir pereina iš vieno „Flip-Flop“ į kitą su kiekvienu poslinkio impulsu (laikrodžio signalas).Kiekvienas „Flip-Flop“ saugo ir perduoda duomenis žingsnis po žingsnio.Šis duomenų perdavimo metodas vadinamas nuosekliuoju ryšiu.Jis dažniausiai naudojamas tokiose sistemose kaip LED tvarkyklės, UARTS (universalūs asinchroniniai imtuvo perrašymai) ir signalo generatoriai.Tokie pamainų registrai taip pat gali būti tobulinami, pavyzdžiui, dvikrypčiai ar apskrito tipai specialioms užduotims, tokioms kaip kodavimo duomenys arba pridedant vėlavimus.Kadangi duomenys juda kontroliuojamu, šiek tiek bitų būdu, ši sąranka yra veiksminga įrenginiams, kurių pralaidumas yra ribotas, arba dideli atstumai, norint siųsti signalus.

Dažnio padalijimas

8 paveikslas. Dažnio padalijimas

Paveikslėlyje parodyta, kaip D flip-flop gali padalyti įvesties dažnį.Prijungiant Q 'išvestį atgal į D įvestį, „Flip-Flop“ perjungia savo būseną kiekviename laikrodžio impulse.Dėl to išėjimo dažnis tampa puse įvesties dažnio (f/2).Šis metodas dažnai naudojamas dažnio dalikliams kurti.Sujungę daugiau „flip-flops“, galite sukurti „Tvent-By-4“, „Padalijimą pagal-8“ ar „Aukštesnes padalijimus“, naudingą skaitmeniniuose laikrodžiuose, „Baud“ greičio generatoriuose ir mėginių ėmimo grandinėse.Šis požiūris yra paprastas, patikimas ir naudojamas minimalia aparatūra, todėl ji yra ideali tvarkant laiką skaitmeninėse sistemose.

Skaitikliai ir laikmačiai

D Flip-Flops yra skaitmeninių skaitiklių ir laiko grandinių elementai.Kai jie yra išdėstyti nuosekliai, jie gali sudaryti dvejetainius ar dešimtmečio skaitiklius, kurie padidina jų išvestį kiekvienu laikrodžio impulsu.Šie skaitikliai yra plačiai naudojami skaitmeniniuose laikrodžiuose, dažnių skaitikliuose ir laikmačio grandinėse, kad būtų galima išmatuoti praėjusį laiką, suskaičiuoti įvykius arba generuoti laiko valdymo signalus.Laikmačio programose „Flip-Flops“ padeda sukurti tikslų vėlavimą padalijant laikrodžio dažnį į ilgesnius, labiau valdomus intervalus.Dėl jų kraštų sukelto pobūdžio D flip-Flops užtikrina, kad skaičiavimas ir laiko perėjimai įvyksta tiksliai tinkamais momentais, sumažinant trikdžių riziką ar laiko klaidas jautriose grandinėse.

Ryšys ir autobusų sąsaja

Skaitmeninių ryšių sistemose duomenis dažnai reikia saugoti laikinai, sinchronizuoti arba pasislinkti tarp komponentų, veikiančių skirtingu greičiu.D Flip-Flops vaidina svarbų vaidmenį atliekant šias užduotis.Jie naudojami „Shift“ registruose, norint konvertuoti duomenis tarp nuosekliųjų ir lygiagrečių formatų tokiuose protokoluose kaip UART, SPI ir I²C.Be to, sąveikoje su autobusais, „D flip-Flops“ padeda užfiksuoti duomenis pervedimo metu, užtikrinant, kad informacija būtų laikoma pastovi pakankamai ilgai, kad ją būtų galima perskaityti ar parašyti per autobusų liniją.Jie taip pat padeda pašalinti laiko neatitikimus tarp skirtingų sistemos dalių, todėl komunikacija tampa patikimesnė, ypač sistemose, kuriose yra keli prietaisai dalijantis duomenų linijomis.

Įterptos sistemos

Įterptosiose programose „D Flip-Flops“ yra naudojami valdymo signalams saugoti, užrakto jutiklių įvestis ir sekti skaitmeninių posistemių būklę mikrovaldikliuose ar procesoriuose.Jų gebėjimas palaikyti duomenis iki kito laikrodžio ciklo užtikrina stabilų veikimą, net dirbant su triukšmingais ar greitai kintančiais signalais.D Flip-Flops padeda tai pasiekti, palaikydami nuspėjamų loginių grandinių, įskaitant būsenos mašinas, sekų valdiklius ir laiko nustatymo grandines, sukūrimą.Jie taip pat naudojami generuojant impulsus, signalus, susijusius su signalais ir sinchronizuojant įvykius.

„D flip-Flops“ pranašumai

• Vieno duomenų įvestis (D)

D Flip-Flops pasižymi vienu duomenų įvestimi, žinomu tiesiog kaip „D“, kuris supaprastina skaitmeninės grandinės dizainą.Skirtingai nuo SR ar JK Flip-Flops, kuriems reikalingi keli įėjimai ir pridėta logika, kad būtų galima valdyti skirtingas būsenas, „D Flip-Flop“ veikia tik su vienu duomenų įvestimi ir laikrodžio signalu.Tai sumažina projektavimo sudėtingumą, sumažina logikos priskyrimo klaidas ir supaprastina signalo maršruto nustatymą integruotose grandinėse.Tai yra naudinga sistemoms, kurioms reikia tikslaus duomenų valdymo, tokių kaip registrai, atminties vienetai ir laiko kritiniai dizainai.

• Vengviuoju valstybių vengimu

Pagrindinis „D flip-Flops“ stiprumas yra jų gebėjimas išvengti neapibrėžtų būsenų-tai bendra SR Flip-Flops problema, kai tiek rinkinys, tiek atstatymas yra įjungiami vienu metu.D „Flip-Flops“, naudodamiesi logine inversija tarp vidinių valdymo signalų, užtikrindami, kad vienu metu aktyviai veiktų tik viena valdymo sąlyga.Šis dizaino pasirinkimas padidina patikimumą ir nuoseklumą, svarbų saugos ar didelio tikslumo aplinkoje.

• Mažesnis energijos naudojimas

„D Flip-Flops“ yra efektyvus energiją, todėl jie yra idealūs mažos galios programoms, tokioms kaip nešiojama elektronika ir akumuliatorių valdomi įrenginiai.Jie dažnai naudoja sąlyginį laikiklį (aktyvina tik keičiant duomenis) ir kitus optimizavimus, kad sumažintų nereikalingą perjungimą, mažindami energijos suvartojimą.Turėdami mažiau vidinių vartų, palyginti su sudėtingesniais Flip-Flops, pavyzdžiui, JK tipu, jie taip pat sumažina statinį ir dinaminį galios praradimą.

• Stabilus dviejų valstybių elgesys

Kaip ir visuose „Flip-Flops“, „D Flip-Flops“ veikia dvipusiai stabiliai, jie gali laikyti vieną iš dviejų išvesties būsenų (0 arba 1), kol kitas laikrodžio signalas paskatins pasikeisti.Tai leidžia jiems veikti kaip vieno bitų atminties vienetus, skirtus nuosekliajai logikai, „Shift“ registrams, skaitikliams ir būsenoms.Jų gebėjimas išlaikyti duomenis be nuolatinio gaivinimo padeda išlaikyti patikimą kontrolės srautą skaitmeninėse grandinėse.

• Paprasta vidinė struktūra

Vidinė D flip-flop konfigūracija yra gana paprasta, dažnai susidedanti iš SR skląsčių ir keitiklio laiko tikslumui.Tai prieštarauja JK arba T Flip-Flops, kuriems reikalingas sudėtingesnis grįžtamasis ryšys ir valdymo logika.„D Flip-Flops“ paprastumas leidžia juos lengviau įgyvendinti, patikrinti ir derinti, o nuspėjamas elgesys daro juos geriausiu pasirinkimu automatiniuose projektavimo procesuose.

• Greitaeigis veikimas

Sukurtas našumui, „D Flip-Flops“ siūlo minimalų sklidimo vėlavimą dėl efektyvaus vidinės grandinės ir greito logikos perjungimo.Tai daro juos idealiais spartų programoms, tokioms kaip skaitmeninio signalo apdorojimo ir ryšių protokolai.Jų krašto sukeltas pobūdis užtikrina tikslią sinchronizaciją su laikrodžio signalais.

• Komponentų efektyvumas

D Flip-Flops yra efektyvus ištekliams, reikalaujant mažiau loginių vartų ir tranzistorių nei kitų tipų.Šis kompaktiškas dizainas reiškia mažesnę lustų plotą, sumažėjusias išlaidas ir didesnio integracijos tankio ICS galimybes.Jų minimalus komponentų naudojimas taip pat lemia mažesnį parazitinį poveikį, padidindamas tiek greičio, tiek energijos vartojimo efektyvumą didelio masto ir aukštos kokybės skaitmeninėms sistemoms.

D Flip-Flops trūkumai

• Vidinių grįžtamojo ryšio mechanizmų nebuvimas

D Flip-Flops yra sukurti tam, kad būtų galima saugoti vieną duomenis, pagrįstus vien tik įvesties ir laikrodžio signalais, ir neturi jokių būdingų grįžtamojo ryšio galimybių.Tai reiškia, kad jie negali pakoreguoti savo išvesties pagal ankstesnes būsenas ar vidinę logiką.Taikant programas, kuriose reikalingi grįžtamasis ryšys, pavyzdžiui, variklio valdymo sistemos, PID kilpos ar adaptyvus filtravimas, turi būti įvesta išorinė grandinė, kad būtų galima imituoti grįžtamąjį ryšį.Pavyzdžiui, išvesties prijungimas prie loginių vartų padidina sudėtingumą, padidina komponentų skaičių ir apsunkina laiko analizę, potencialiai sumažinant sistemos reagavimą ir stabilumą.

• Nėra gimtojo perjungimo funkcijos

D Flip-Flops iš prigimties neperkalba jų išvesties su kiekvienu laikrodžio impulsu;Vietoj to, jie atspindi įvestį ant laikrodžio sujungimo krašto.Tai daro juos netinkamus tiesiogiai naudoti skaitikliuose ar dažnio dalikliuose, kur reikia perjungti elgesį.„T flip-Flop“ imituojant apverstą išvestį prie duomenų įvesties, tačiau tai prideda papildomo laidų, padidina jautrumą signalo vientisumo problemoms ir reikalauja kruopštaus laiko, kad būtų išvengta lenktynių sąlygų, ypač problemiškų greitųjų grandinėje.

• Plokštės vėlavimas

Kaip ir visi „Flip-Flops“, D tipai įveda sklidimo uždelsimą, laiką tarp laikrodžio krašto ir atitinkamo išvesties pokyčio.Nors dažnai nanosekundžių diapazone, šis delsimas gali kauptis greitaeigių ar giliai vamzdynų sistemose, gali sukelti laiko pažeidimus, trūkumus ar iškrypimus.Tiksli laiko analizė, dažnai naudojant modeliavimo įrankius ir išsamias laiko nustatymo schemas, naudojama tokiuose dizainuose, kad būtų užtikrintas stabilumas ir teisingumas.

• Nustatykite ir palaikykite laiko jautrumą

D Flip-Flops reikalauja, kad duomenų įvestis išliktų stabilus trumpam langui prieš ir po laikrodžio krašto, žinomo kaip sąranka ir palaikymo laikas.Jei šis reikalavimas pažeidžiamas, pavyzdžiui, kai duomenų perėjimai vyksta per arti laikrodžio, gali atsirasti klaidingų ar nenuspėjamų išėjimų.Didelės spartos ar sudėtingo dizaino metu šie laiko apribojimai gali būti sudėtingi, dažnai reikalaujant naudoti buferius ar kruopštų kelio balansavimą, padidinti projektavimo sudėtingumą ir sumažinti laiko ribas.

• Metastalumo rizika

MetaSTUMPLESS atsiranda tada, kai „Flip-Flop“ įvesties perėjimus gauna per arti laikrodžio krašto, dažnai iš asinchroninių šaltinių, todėl jis pateko į nestabilią būseną, kuriai išspręsti gali prireikti laiko.Šiuo laikotarpiu išvestis gali svyruoti arba sukelti neapibrėžtą loginį lygį.Tai pavojinga sistemose, kuriose svarbus deterministinis elgesys, pavyzdžiui, kertant laikrodžio domenus.Norėdami tai sušvelninti, naudokite sinchronizatorių grandines arba „Flip-Flops“, skirtus grakščiai valdyti metastomumą.

• Ribota integruota funkcija

Nors „D Flip-Flops“ yra paprastas ir plačiai naudojamas, siūlo tik pagrindines duomenų saugojimo funkcijas.Priešingai, JK arba SR FLIP-FLOPS palaiko sudėtingesnes operacijas, tokias kaip perjungimas ar vienu metu nustatytos/iš naujo nustatytos sąlygos be papildomos logikos.D Flip-Flops taip pat dažnai trūksta asinchroninio išankstinio nustatymo ir aiškių įvesties, nebent tai būtų specialiai sukurta, ribojant jų lankstumą tam tikruose kontrolės scenarijuose.Programoms, kurioms reikalingas didesnis niuansuotas elgesys per vieną laikrodžio ciklą, papildomi vartai ir logika turi papildyti D flip-Flops, padidinant grandinės sudėtingumą ir projektavimo pastangas.

Išvada

D Flip-Flops yra labai naudingi skaitmeninėje elektronikoje, nes jie gali saugoti duomenis ir išlaikyti juos stabilius, naudodami laikrodžio signalus.Juos paprasta naudoti, venkite klaidų, tokių kaip netinkamos būsenos, ir gerai veikia greitos ir mažos galios sistemose.Galite juos naudoti registruose, skląsčiuose, skaitikliuose ir duomenų perdavimo grandinėse.Jie taip pat yra naudingi tokiose sistemose kaip mikrovaldikliai ir ryšių įrenginiai.Tačiau jie turi keletą trūkumų, tokių kaip vėlavimai reaguojant į laiką, reikia kruopštaus laiko ir neuždengdami grįžtamojo ryšio ar perjunkite funkcijas.Žinant tiek stipriąsias, tiek silpnąsias puses padeda kurti geresnes skaitmenines sistemas.

Apie mus

ALLELCO LIMITED

Skaityti daugiau

Greitas užklausa

Prašau atsiųsti užklausą, mes nedelsdami atsakysime.

Dažnai užduodami klausimai [FAQ]

1. Kokia yra standartinė D flip-flop forma?

„D flip-flop“ turi tris pagrindines dalis: duomenų įvestį (D), laikrodžio įvestį (CLK) ir du išėjimus (q ir q ′).Jis veikia nukopijuodamas vertę nuo D įvesties į Q išvestį tik tada, kai keičiasi laikrodžio signalas, paprastai kylančiame krašte (nuo žemos iki aukšto).Po to momento išvestis išlieka tokia pati, net jei įvestis keičiasi.Dėl šios sąrankos „D flip-Flop“ yra naudingas tam, kad būtų galima saugoti vieną informaciją tam tikru metu.Standartinis „D flip-flop“ yra paprastas ir patikimas, todėl jis yra įprastas atminties grandinėse ir skaitmeninėse sistemose.

2. Kokia yra d flip-flops lygtis?

Pagrindinė „D flip-Flop“ taisyklė yra paprasta: išėjimo q tampa lygus įvestiei d, kai keičiasi laikrodžio signalas.Tai galima parašyti kaip q (kitas) = D. Tai reiškia, kad ir kokia vertė yra D įvesties metu tuo metu, kai laikrodžio kraštas įvyksta, perduodamas Q išvesčiai.„Flip-Flop“ nepaiso visų kitų pakeitimų iki kito laikrodžio krašto.Tai leidžia „D flip-Flops“ lengvai naudoti ir suprasti skaitmeniniuose dizainuose.

3. Koks yra d flip-flop išėjimo dažnis?

Jei D įvestį prijungsite prie Q išėjimo priešingybės (Q ′), „D flip-flop“ perjungs savo būseną kiekvieną kartą, kai laikrodžio signalas erkės.Tai daro išvesties dažnį pusę laikrodžio dažnio.Taigi, jei laikrodis yra 8 MHz, išėjimas tampa 4 MHz.Ši sąranka dažnai naudojama grandinėse, kad būtų galima padalyti dažnį, pavyzdžiui, laikmačiuose ar skaitikliuose.

4. Kuo skiriasi D ir T Flip-Flops?

D flip-flop nukopijuoja įvestį (d) į išvestį (q), kai keičiasi laikrodis.Jis naudojamas duomenų saugojimui.„T Flip-Flop“ veikia skirtingai, jis keičiasi arba „perjungia“ savo išvestį kiekvieną kartą, kai laikrodis pažymi, bet tik tuo atveju, jei T įvestis yra aukštas.Jei t yra žemas, nieko neatsitiks.D Flip-Flops naudojami duomenims laikyti, o „T Flip-Flops“ yra naudojami statant skaitiklius ir padalyti laikrodžio signalus.Jie elgiasi skirtingai, nors abu sukelia laikrodis.

5. Kuo skiriasi „AT“ ir „D Flip-Flop“?

Nėra standartinio „flip-flop“, vadinamo „Flip-flop“.Tai gali būti klaida ar rašybos klaida, galbūt skirta pasakyti „t flip-flop“.Tokiu atveju skirtumas yra paprastas: D flip-flop saugo D įvesties vertę, kai laikrodis pažymi, o „T flip-flop“ perjungia jo išvestį (perjungia nuo 0 iki 1), jei T įvestis yra aukštas.Taigi, „D Flip-Flops“ yra skirtos duomenų saugoti, o „T Flip-Flops“ yra skirtos perjungti būsenas.Jei „AT“ reiškia ką nors kita, tai reikia aiškiau paaiškinti.

Užpildyta XC4044XL-3BG432C FPGA apžvalga

2025/06/2

Jūsų vadovas apie mpc8247czqtiea iš „Freescale“

2025/05/30

Populiarūs įrašai

-

Sudėtingos instrukcijos Nustatykite kompiuterius: kaip jie pakeitė skaičiavimą?

8000/04/18 147749

-

USB-C PINOUT ir funkcijos

2000/04/18 111921

-

„Xilinx Unified“ modeliavimo primityvų naudojimas: išsamus FPGA projektavimo ir modeliavimo vadovas

1600/04/18 111349

-

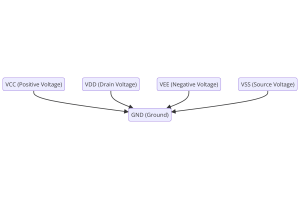

Maitinimo įtampa elektronikoje: VCC, VDD, VEE, VSS ir GND reikšmė

0400/04/18 83714

-

„RJ45“ jungties vadovas: „Pmout“, laidų, laidų tipai ir naudojimas

1970/01/1 79502

-

Pagrindinis vielos spalvų kodų vadovas šiuolaikinėse elektrinėse sistemose

Tai, kaip mūsų elektros sistemos naudoja spalvas, nėra tik išvaizdos.Kiekviena vielos spalva dabar rodo konkrečią funkciją, todėl montavimo ir priežiūros metu lengviau nustatyti ir tvarkyti elektro...1970/01/1 66872

-

Kokybės (Q) faktorius: lygtys ir programos

Kokybės koeficientas, arba „Q“, yra svarbus tikrinant, kaip gerai induktoriai ir rezonatoriai veikia elektroninėse sistemose, kuriose naudojami radijo dažniai (RF).„Q“ matuoja, kaip gerai grandinė ...1970/01/1 63005

-

Išvalymo vožtuvo vadovas: funkcija, simptomai, testavimas ir pakeitimas, kad būtų galima optimaliai atlikti variklio veikimą

Išvalymo vožtuvas yra pagrindinė automobilio sistemos dalis, padedanti išlaikyti orą švarų, valdant degalų garus, kol jie gali ištrūkti į atmosferą.Tai ne tik padeda aplinkai sumažinti taršą, bet i...1970/01/1 62954

-

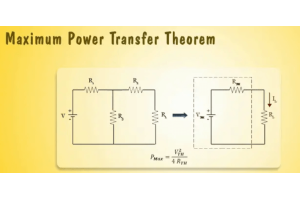

Pasiekti maksimalų našumą naudojant maksimalios galios perdavimo teoremą

Maksimalios galios perdavimo teorema paaiškina, kaip energija iš šaltinio, pavyzdžiui, akumuliatorius ar generatorius, teka į prijungtą apkrovą.Tai parodo tikslią sąlygą, kai apkrova gauna daugiaus...1970/01/1 54078

-

A23 akumuliatoriaus specifikacijos ir suderinamumas

„A23“ baterija yra maža, cilindro formos akumuliatorius, turintis aukštą įtampą.Taip pat vadinamas 23A, 23AE arba MN21, jis veikia esant 12 voltų ir daug aukštesnis nei AA ar AAA baterijos...1970/01/1 52092