2024/05/10

599

Išsamus viso priedo vadovas

Skaitmeninės elektronikos ir kompiuterių inžinerijos srityje priedai yra vienas iš svarbiausių elementų, esminių statybinių ir sudėtingesnių aritmetinių grandinių statybose ir funkcionalumuose.Kaip neatsiejami aritmetinio loginio bloko (ALU) komponentai, priedai palengvina daugybę skaičiavimo operacijų, pradedant nuo pagrindinių aritmetinių iki sudėtingų loginių užduočių, reikalingų sistemos operacijoms.Jų dizainas, kuris gali skirtis nuo paprastų pusiau tiekėjų iki sudėtingesnių pilnų priedų, vaidina lemiamą vaidmenį didinant efektyvumą ir perdirbimo greitį skaitmeninėse sistemose.Šis straipsnis gilinasi į išsamią įvairių tipų priedų architektūrą ir funkcinius niuansus, iliustruojančius jų kritinį vaidmenį šiuolaikinėje skaičiavimo technologijoje ir tyrinėjant jų veiklos logiką, schemas ir programas platesniame skaitmeninės logikos dizaino kontekste.

Katalogas

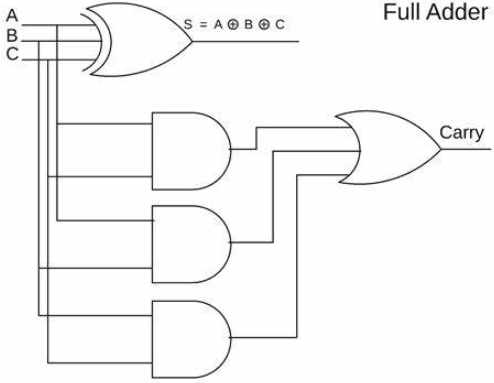

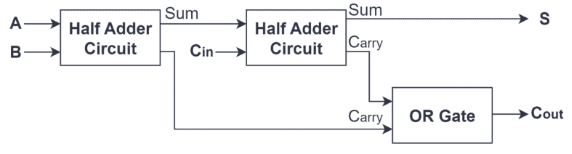

1 paveikslas: Visas priedas

„Broed“ yra pagrindinis elektroninės inžinerijos ir skaitmeninės logikos dizaino komponentas, kuris vaidina pagrindinį vaidmenį sudėtingesnėse kompiuterinėse sistemose.Kaip aritmetinio loginio bloko (ALU) dalis, „BroDder“ tvarko įvairias būtiniausias skaičiavimo užduotis.Viso procesoriaus efektyvumą ir našumą daro tiesioginis poveikis „Broed“ projektavimui ir funkcionalumui.

Procesoriuje pridėjimas naudojamas ne tik pagrindinėms aritmetinėms operacijoms, tokioms kaip papildymas ir atimtis, bet ir įtraukia platesnį loginių operacijų spektrą.Pavyzdžiui, vykdydamas programas, procesoriui dažnai reikia apskaičiuoti naujus atminties adresus.Paprastai tai daroma pridedant prie dabartinio adreso arba atimant iš jų - tai užduotis, kurią atlieka Bendras.Jie kontroliuoja kilpų iteracijų skaičių ir bendrą srautą padidindami ir mažindami skaitiklius.Sudėtingesnėse programose, tokiose kaip lentelės indeksavimas, priedai greitai nustato duomenis apskaičiuodami poslinkius.Tai svarbu duomenų bazių valdymo sistemoms, kompiliatorių konstrukcijai ir didelio masto duomenų apdorojimui.Adderiai taip pat yra svarbiausia įgyvendinant tam tikrus žemėlapių sudarymo metodus daugiapakopių talpyklų sistemose, naudojant aritmetines operacijas, kad nustatytų duomenų talpyklos padėtį ir taip optimizuotų prieigos efektyvumą.

Technologiškai priedai įgyvendinami naudojant įvairius grandinių dizainus, įskaitant paralelius, serijinius ir vamzdynų priedus.Lygiagrečiai priedai yra palankūs dėl jų galimybių vienu metu tvarkyti kelis skaitmenis, todėl jie yra tinkami scenarijams, kuriems reikalingas greitas skaičiavimas.Kita vertus, serijiniai priedai apdoroja po truputį per laikrodžio ciklą ir yra idealūs ribotoms ištekliams ar mažos galios aplinkai.Vamzdynų priedai padalija papildymo procesą į keletą etapų, kiekviename tvarko dalį papildymo operacijos.Šis dizainas žymiai padidina skaičiavimo greitį, ypač aukšto našumo skaičiavimo aplinkoje.

Pusiau Adder grandinė yra pagrindinis skaitmeninės elektronikos elementas, specialiai sukurtas pridėti du dvejetainius skaitmenis.Ši grandinė yra viso priedo pagrindas ir yra raktas norint suprasti sudėtingesnius logikos grandinės dizainus.Per pusę papildymo yra du pirminiai įėjimai, pažymėti A ir B, kurie atspindi atitinkamai Augend ir priedą.Ši sąranka suteikia galimybę apskaičiuoti sumą ir nešiotis išvestį, nereikalaujant ankstesnių skaičiavimų įvesties.

Pusiau adderio šerdį sudaro du loginiai vartai: XOR vartai ir vartai.„XOR“ vartai yra atsakingi už sumos išvesties generavimą.Jis veikia pagal paprastą taisyklę, kai ji išveda 1, jei tik vienas iš jo įvestų yra 1;Priešingu atveju jis išleidžia 0 ir vartus, kita vertus, tvarko nešiojimo išvestį.Jis sukuria 1 tik tada, kai abu jo įėjimai yra 1, puikiai suderina su pagrindiniais dvejetainio pridėjimo reikalavimais.

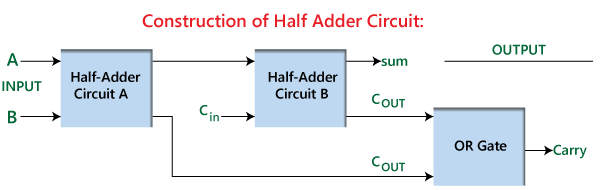

2 paveikslas: Pusės priedo konstrukcija

Šis efektyvus ir paprastas dizainas leidžia pusmetį ne tik savarankiškai atlikti pagrindinį dvejetainį papildymą, bet ir būti statybinis blokas, skirtas sukurti visą papildymą.Visas priedas sukonstruotas derinant du pusės priedus su papildomais ar vartais.Šioje sąrankoje pirmasis pusės priedas užima pradinę papildymo užduotį, sukuriant preliminarią sumą ir nešiojant.Tada antrosios pusės priedas apdoroja nešiojimą nuo pirmojo kartu su papildomu nešiojimo įvestimi.Galiausiai OR vartai sujungia du nešiojimo išėjimus, kad būtų galima gauti galutinį nešiojimo išvestį.Šis išdėstymas pagerina „Broed“ funkcionalumą, leidžiantį jam atlikti sudėtingesnes kelių bitų papildymo užduotis, parodant plačiai paplitusią pritaikymą ir pusės priedų svarbą skaitmeninės grandinės projektavime.

Visas priedas yra pažengęs skaitmeninės logikos dizaino komponentas, įrengtas taip, kad būtų galima pridėti tris vieno bitų dvejetainius įėjimus, paprastai pažymėtus kaip A, B ir „Carry-In“ (CIN).Šis dizainas leidžia visam papildymui efektyviai apdoroti sudėtingus dvejetainius papildymus, į vieną operaciją įtraukiant ankstesnių žemesnės eilės skaičiavimų nešimą.

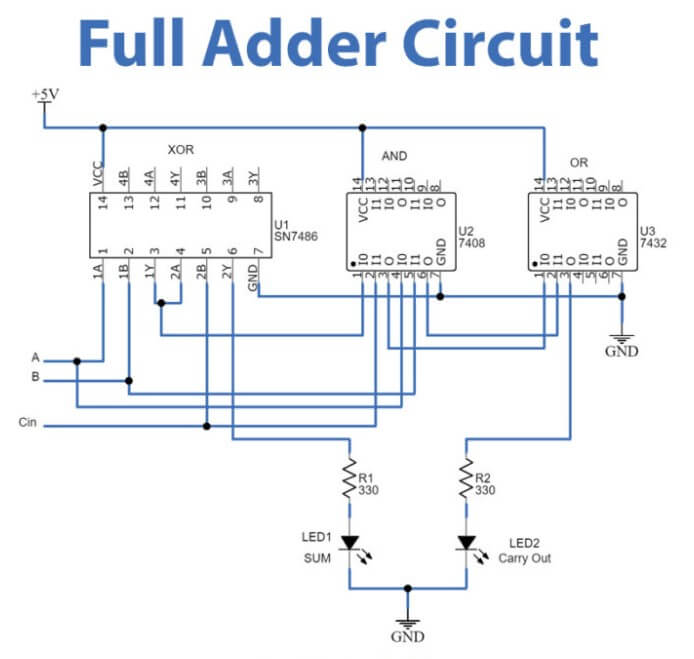

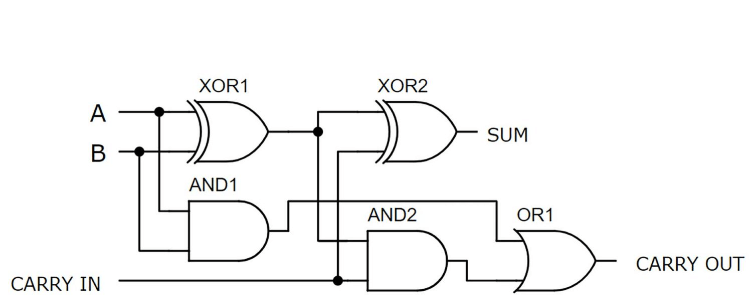

3 paveikslas: Visa priedo grandinė

Funkciniu požiūriu visas priedas gali išvesti dvigubą sumą, o tai reiškia, kad jo išėjimas gali svyruoti nuo 0 iki 3, be to, jis taip pat gali pagaminti pernešimą (COUT).Taip atsitinka todėl, kad kai visi įvesties bitai yra nustatyti iki 1 (a = 1, b = 1, cin = 1), sumos išėjimas bus 1 (žymi dvejetainį 01) ir sugeneruotas 1 išėjimas, tai rodo, kad tai rodo, kad tai rodo, kad tai rodo, kad tai rodo, kad tai rodo, kad tai rodo, kad tai rodoPapildomą nešiojimą reikia perduoti kitam aukštesniam bitui.

Struktūriškai visą papildymą paprastai sudaro dvi pusės priedai ir vienas ar vartai.Pirmojo pusės priedas užima įvestis A ir B, sukuriant pradinę sumą ir nešiojimo signalą.Tada ši pradinė suma, kartu su nešiojimu (CIN), į antrąjį pusmetį.Antrosios pusės papildymo vaidmuo yra pridėti šią sumą nuo pirmosios pusės „Cin“, pagaminant kitą sumą ir naują perkėlimo išvestį.Tuo pačiu metu nešiojimo išėjimas iš pirmosios pusės papildymo ir pernešimo iš antrosios pusės priedo sujungiamas per arba vartus, kurių kulminacija yra viso to, kas galutinai perkeliama (COUT).Šios konstrukcijos dizainas užtikrina, kad visas papildymas veiksmingai tvarko nešiklių sklidimą papildomomis operacijomis, todėl jis yra idealus vykdant daugialypius dvejetainius papildymus.Taigi, viso papildymo dizainas ne tik pagreitina duomenų apdorojimą ir padidina efektyvumą, bet ir supaprastina aparatinės įrangos įgyvendinimo sudėtingumą per tiesioginį loginių vartų derinį, todėl tai yra nepakeičiamas komponentas, susijęs su kelių skaitmenų papildymu ir aritmetiniu loginiu vienetu (ALU).

|

Parametrai

|

Pusė priedo

|

Visas priedas

|

|

Aprašymas

|

Pusė priedo yra kombinuota logika

grandinė, pridedanti du 1 bitų skaitmenis.Pusiau siegas sukuria abu sumą

įvestys.

|

Visas priedas yra kombinuota logika

Grandinė, atliekanti papildomą operaciją trijuose vieno bitų dvejetainiuose numeriuose.

Visas priedas sukuria trijų įvesties ir nešiojimo vertę.

|

|

Ankstesnis nešimas

|

Ankstesnis nešiojimas nenaudojamas.

|

Naudojamas ankstesnis nešiojimas.

|

|

Įvestys

|

Pusiau priede yra du įvesties bitai (a,

B).

|

Visiškame papildyme yra trys įvesties bitai

(A, b, cį).

|

|

Išėjimai

|

Sukurtas išėjimas yra dviejų bitų sumos

ir pernešti iš 2 bitų įvesties.

|

Sukurtas išėjimas yra dviejų bitų sumos

ir pernešti iš 3 bitų įvesties.

|

|

Naudojamas kaip

|

Pusės patalpos grandinės negalima naudoti

Lygiai taip pat, kaip ir viso priedo grandinė.

|

Vietoje gali būti naudojama visa papildymo grandinė

pusės priedo grandinės.

|

|

Savybė

|

Tai paprasta ir lengva įgyvendinti

|

Viso priedo dizainas nėra toks

Paprasta kaip pusė priedo.

|

|

Loginė išraiška

|

Loginė pusės priedo išraiška yra:

S = a⊕b;C = a*b.

|

Loginė viso priedo išraiška yra:

S = a⊕b⊕cin;Cout= (a*b)+(cį*(a⊕b)).

|

|

Loginiai vartai

|

Jį sudaro vienas iš Ex-Or vartų ir vienas ir

vartai.

|

Jį sudaro du ex-arba du ir vartai,

ir vienas ar vartai.

|

|

Paraiškos

|

Jis naudojamas skaičiuotuvuose, kompiuteriuose,

Skaitmeniniai matavimo įtaisai ir kt.

|

Jis naudojamas keliuose bitų papildymuose,

Skaitmeniniai perdirbėjai ir kt.

|

|

Alternatyvus vardas

|

Nėra pakaitinio pavadinimo pusei

Privalumas.

|

Visas priedas taip pat žinomas kaip „Ripple-Carry“

Privalumas.

|

Diagrama

1: Skirtumas tarp pusės ir pilno priedo

Viso papildymo tiesos lentelė yra raktas norint suprasti jo veiklos logiką, išsamiai aprašant tikslų ryšį tarp dvejetainių įvesties derinių ir atitinkamų jų išėjimų.Ši lentelė parodo visus galimus įvesties scenarijus ir jų rezultatus, todėl tai yra esminė priemonė projektuojant ir tikrinant skaitmeninių loginių grandinių.Visas priedas apdoroja tris įvestis: A, B ir A Derve (CIN), kurių kiekvienas gali būti 0 arba 1. Tai lemia aštuonis įmanomus įvesties derinius.

Kiekvieno iš šių derinių išėjimai iš viso papildymo apima sumą (sumą) ir išvežimą (COUT).Suma yra trijų įvesties-B ir CIN-modulio-2 (XOR operacija).Perkėlimas įvyksta tada, kai bent du iš įvesties bitai yra 1. Tai atspindi visą papildymo galimybes tvarkyti pernešimą nuosekliomis papildymo operacijomis, užtikrinant aukštesnio bitų skaičiavimų tikslumą.

Norėdami iliustruoti, apsvarstykite įvesties scenarijų, kai visi įėjimai yra 0 (a = 0, b = 0, c-in = 0).Išėjimo suma bus 0, o nešiojimas taip pat bus 0, tai rodo, kad nėra papildomos sumos ar nešiolio valdymo.Jei tik vienas įvesties bitas yra 1, pavyzdžiui, a = 1, b = 0, c-in = 0, išvesties suma bus 1 be nešiolio, parodydama, kad nereikia perkelti nešiojimo į didesnį bitą.Kai du įvesties bitai yra 1, pavyzdžiui, a = 1, b = 1, c-in = 0, išvestiIšsitraukimas yra 1, nurodant nešiojamąjį nešiojimą, kurį reikia perduoti kitam aukštesniam bitui.Sudėgiausias scenarijus įvyksta, kai visi trys įvesties bitai yra 1 (a = 1, b = 1, c-in = 1);Išėjimo suma yra 1, o yra 1, kas rodo, kad perkėlimo valdymas taip pat gali būti reikalingas dar aukštesniuose bituose.

|

A

|

B

|

Cį

|

S

|

Cout

|

|

0

|

0

|

0

|

0

|

0

|

|

0

|

0

|

1

|

1

|

0

|

|

0

|

1

|

0

|

1

|

0

|

|

0

|

1

|

1

|

0

|

1

|

|

1

|

0

|

0

|

1

|

0

|

|

1

|

0

|

1

|

0

|

1

|

|

1

|

1

|

0

|

0

|

1

|

|

1

|

1

|

1

|

1

|

1

|

2 diagrama: pilna „Adder“ tiesos lentelė

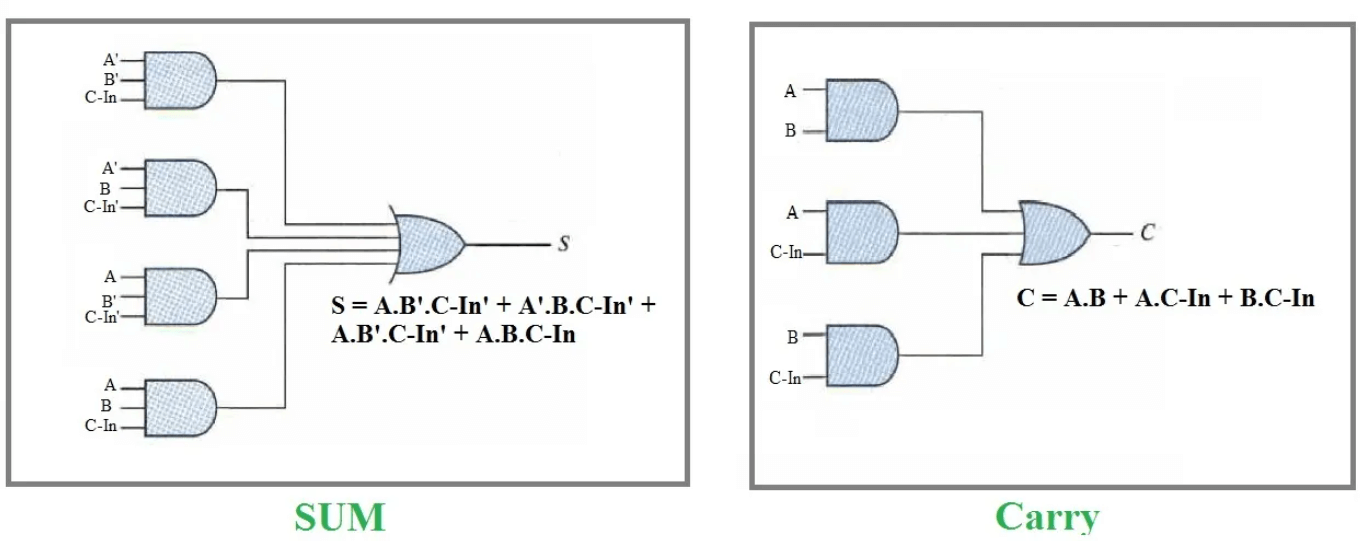

Viso papildymo supratimas apima jo funkcionalumo išskaidymą naudojant tiesos lentelę, kur skirtingos įvesties verčių deriniai A, B ir C-IN lemia išvestų sumą ir COUT.Norėdami suvokti operaciją, žingsnis po žingsnio supaprastiname logines lygtis.

Loginė išraiška sumai

Lygtis prasideda atskirais atvejais, kai suma lygi 1:

• A 'B' CIN + A 'B CIN' + A B 'CIN' + AB CIN

Šią lygtį galima sutrumpinti suskirstant terminus su CIN ir be jo:

• cin (a 'b' + ab) + cin '(a' b + a b ')

Šis supaprastinimas lemia lengviau įgyvendinamą formą:

• CIN XOR (A XOR B)

Šis vaizdas rodo, kad sumos išvestis iš esmės yra XOR operacija tarp A, B ir CIN, užfiksuojant dvejetainio papildymo pagrindinį elgesį, kai sumos perjungimai, pagrįsti nelyginiu skaičiumi.

COUT logika

Pradedant nuo sąlygų, kuriose sukuriamas nešimas:

• A 'B CIN + A B' CIN + AB C-In ' + AB CIN

Supaprastindami lygtį, mes nustatome terminus, kurie paprastai apima nešiojimo generavimą:

• AB + B CIN + A CIN

Ieškant kito COOT įgyvendinimo būdo, lygtis gali būti pertvarkyta:

• ab + a cin + b c-in (a + a ')

Tai plečiasi ir rekombinuoja, kad būtų užfiksuoti visi scenarijai, kai bent du įvestys yra 1:

• AB CIN + AB + A C-in + A 'B CIN

• AB (1 + cin) + a c-in + a 'b cin

• ab + a c-in (b + b ') + a' b cin

• ab + a b 'cin + a' b cin

• ab + cin (a 'b + a b')

Galutinė kompaktiška COUT forma:

• AB + CIN (A XOR B)

Ši „Carry-Out“ lygties versija parodo, kaip COUT gaminamas, kai ir A, ir B yra 1, arba kai vienas iš A arba B yra 1 kartu su nešiojimu, tokiu būdu apima logiką, reikalingą pernešimo sklidimui valdyti daugialypėje dalyjeBIT dvejetainis papildymas.Ši supaprastinta logika yra ypač naudinga įgyvendinant efektyvias skaitmenines grandines.

4 paveikslas: Viso papildymo lygtys

Įdiegus visą „Bround“ grandinę, reikia kruopščiai surinkti du pusę priedų ir ar vartų, kad būtų sukurtas įrenginys, galintis efektyviai tvarkyti tris vienkartinius dvejetainius įėjimus.Šis išdėstymas optimizuoja grandinės sudėtingumą ir užtikrina tiek efektyvius, tiek tikslius skaičiavimus.

Norėdami pradėti, pirmasis pusės priedas užima du pirminius dvejetainius įėjimus, A ir B, kurie yra pagrindiniai skaitmenys, kuriuos reikia pridėti.Pagrindinė jos užduotis yra apskaičiuoti sumą ir pradinį šių dviejų skaičių nešimą.Čia pirmoji pusė pateikia du rezultatus: pradinę sumą (SUM1) ir pradinį nešiojimą (nešiojama1).Sum1 yra gaunamas iš A ir B operacijos, nurodant, ar bendra dalis turi nelyginį skaičių 1.„Carry1“, veikimo tarp A ir B rezultatas rodo, ar abu skaitmenys yra 1, todėl reikia pernešti į kitą aukštesnį bitą.

Toliau prie proceso prisijungia antroji pusė.Kaip jo įvestį jis naudoja sumos išvesties sum1 ir trečiąjį įvesties CIN (perkėlimas iš ankstesnio skaičiavimo).Antrosios pusės priedas sukuria du išėjimus: galutinio sumos rezultatas (SUM2) ir antrinis nešiojimas (nešiojimas2).SUM2, kuris yra XOR rezultatas SUM1 ir CIN, yra galutinė trijų įėjimų suma, parodanti bendrą dvejetainį papildymą.Nešiojimas2, atsirandantis iš Sum1 ir CIN veikimo ir veikimo, rodo šių komponentų sugeneruotą nešiojamąjį nešiojimą.

5 paveikslas: Visa priedo grandinė su dviem pusės priedo naudojimu

Galiausiai, norint užbaigti visą papildymo dizainą, reikia, kad arba vartai būtų tvarkomi nešiojimo išėjimams1 ir nešiojimui2 iš abiejų pusių priedų.Šis arba vartai užtikrina, kad bet kuris skaičiavimų metu sugeneruotas nešimas būtų teisingai persiunčiamas į galutinę išvestį.Todėl visas papildymo galutinis nešiojimo išėjimas (COUT) yra „Carry1“ ir „Carry2“ rezultatas arba rezultatas.Šio ar vartų įtraukimas garantuoja, kad visi potencialūs nešiojimai yra tiksliai apskaičiuojami ir perkeliami į kitą lygį atliekant kelių bitų papildymo operacijas, užtikrinant aritmetinės operacijos vientisumą keliuose bituose.

Visiški priedai vaidina nepakeičiamą vaidmenį skaitmeninės logikos dizaine, siūlydami daugybę privalumų, dėl kurių jie tampa svarbūs įvairiuose skaičiavimo ir duomenų apdorojimo scenarijuose.Pagrindiniai jų pranašumai yra puikus lankstumas, greitas apdorojimo greitis ir efektyvus nešiojimo valdymas.Dėl šių bruožų pilni priedai yra idealūs atliekant sudėtingas aritmetines operacijas ir logines funkcijas, ypač programose, kurioms reikalingas nuoseklus kelių bitų papildymas.

Privalumai

Lankstumas: Pilnos priedai puikiai tinka vienu metu apdoroti kelis dvejetainius įėjimus (A, B ir CIN).Jie taip pat gali būti išplėsti į didesnius papildomųjų matricas, kad būtų galima valdyti ilgesnius dvejetainius skaičius.Šis mastelio keitimas yra svarbus kuriant aukštos kokybės aritmetinius loginius vienetus (ALUS), kurie turi atlikti sudėtingas daugialypis aritmetines ir logines operacijas.

Greitis: Dėl jų vidinio lygiagretaus apdorojimo architektūros, pilni priedai gali užpildyti visus įvestis vienu laikrodžio ciklu, taip pat nustatydami, kad jie nešiotų išėjimus.Ši galimybė palaiko nuolatines papildymo operacijas ir yra būtina realiojo laiko duomenų apdorojimui šiuolaikiniuose mikroprocesoriuose ir greitaeigių skaičiavimo įrenginiuose.

Trūkumai

Tačiau pilni priedai taip pat pateikia pastebimus trūkumus:

Sudėtingumo ir įgyvendinimo sudėtingumas: pilni priedai apima kelis loginius vartus ir daugiapakopį nešiojimo sklidimą, todėl jų dizainas yra sudėtingas.Šis sudėtingumas ne tik padidina gamybos sąnaudas, bet ir gali paveikti grandinių patikimumą.

Dauginimo vėlavimo problemos: Perkelkite dauginimąsi per kelis loginius vartus, kiekvienas padidindamas savo vėlavimą.Tai gali apriboti bendrą skaičiavimo greitį didelio masto operacijų metu, ypač plačiose kompiuterinėse sistemose ir projektuojant labai didelę masto integraciją (VLSI) ir greitaeigius procesorius.Vėlavimas gali tapti reikšmingu atlikimo kliūtimi.

Norėdami sušvelninti šias problemas, inžinieriai nuolat tyrinėja efektyvesnius grandinių dizainus.Strategijos apima greitesnių loginių vartų technologijų naudojimą, grandinių išdėstymo optimizavimą, siekiant sutrumpinti kelio ilgį, ir pažangių technologijų, tokių kaip nešiojamosios išsaugojimo priedai, kūrimas, kad būtų sumažintas nešiojimo sklidimo vėlavimas.

Pilni priedai yra plačiai naudojami skaitmeninėje logikoje, vertinami dėl jų lankstumo ir efektyvumo, todėl jie yra svarbūs daugybei skaičiavimo ir duomenų apdorojimo užduočių.Jų taikymas apima pagrindines aritmetines operacijas iki sudėtingo signalo apdorojimo ir sistemos valdymo.Čia pateikiamas išsamus kai kurių pagrindinių sričių, kuriose pilni priedai yra neatsiejami.

Aritmetinės grandinės

Vienas iš tiesiausių pilnų priedų naudojimo būdų yra aritmetinėse grandinėse, kur jie atlieka dvejetainį papildymą.Ypač labai svarbu pridedant kelių bitų skaičių, pilni priedai valdo ilgesnes dvejetaines sekas per kaskadą.Šioje išdėstyme kiekvienas visas papildymas tvarko savo bitų padėtį ir nešiojimą iš apatinio bitų, tada perduoda naują nešiojimą į kitą aukštesnio bitų pilną priedą.Ši „Cascade“ įgalina išsamų kelių bitų papildymą visame skaitmenų asortimente.

Duomenų apdorojimas

Visiški priedai taip pat vaidina pagrindinį vaidmenį pažengusiose duomenų apdorojimo užduotyse, tokiose kaip skaitmeninio signalo apdorojimas (DSP) filtravimui ir Furjė transformacijoms, kur reikia tikslių ir greitų aritmetinių operacijų.Be to, informacijos saugumo srityje, įskaitant duomenų šifravimo ir klaidų aptikimo bei pataisos algoritmus, tokius kaip pariteto patikrinimai ir ciklinio pertekliaus patikrinimo (CRC) kodo generavimas, pilni priedai yra labai svarbūs atliekant esmines bitų operacijas.

Skaitikliai

Skaitmeniniuose skaitikliuose pilni priedai yra būtini įgyvendinant tiek padidėjimo, tiek mažinimo funkcijas, ypač moduliniuose ir sinchroniniuose skaitikliuose.Jie tiksliai valdo vežimus ir skolinasi, kad būtų užtikrintas tikslus skaičiavimas.

Multiplekseriai (MUX) ir demultiplekseriai (demux)

Multiplekseriuose ir demultiplekseriuose pilni priedai vaidina svarbų vaidmenį pasirinkant kanalą ir paskirstant duomenis.Jie dalyvauja logikoje, nustatančioje, kurie kanalai naudojami duomenų įvedimui ir išvesčiai, priimdami sprendimus, pagrįstus logikos valdymo signalais.

Atminties technologija

Atminties adresams pilni priedai padeda generuoti adresų signalus dinamiškai pasiekti atminties vietas.Tai ypač svarbu dinaminėje atsitiktinės prieigos atmintyje (DRAM) ir kitose saugojimo sistemose, kur pilni priedai palaiko sudėtingus adresų skaičiavimus, kad padidintų prieigos prie atminties efektyvumą.

Aritmetiniai loginiai vienetai (ALU)

Galiausiai, kadangi pagrindiniai aritmetinių loginių vienetų komponentai mikroprocesoriuose ir skaitmeninio signalo procesoriuose, pilni priedai yra labai svarbūs.ALU tvarko visas aritmetines ir logines operacijas, su visais priedais užtikrinant, kad duomenys būtų apdorojami tiek greitai, tiek tiksliai.

Pilnus priedus galima sukurti naudojant įvairius loginius vartus ir konfigūracijas.Čia nagrinėjame keturis skirtingus įgyvendinimus, pabrėždami jų sąranką ir veiklos niuansus.

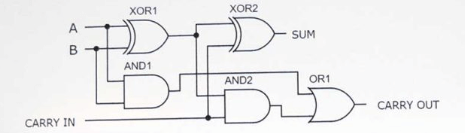

Visas papildymas, pastatytas su XOR, ir arba vartai

6 paveikslas: Visas papildymas, pastatytas su XOR, ir arba Logikos vartai

Šis pavyzdys parodo pilną priedą, pastatytą ant duonos lentos, naudojant atskiras tranzistorius.Konfigūraciją sudaro penki loginiai vartai: du xor vartai, du ir vartai ir vienas ar vartai, iš viso reikia 21 tranzistorių.A ir B įėjimai yra prijungti prie duonos lentos viršutinės kairiosios pusės, gaunančios +5 V tiekimą.Šie įėjimai kontroliuojami naudojant du jungiklius.Du šviesos diodai viršuje kairėje nurodo A ir B įvesties būsenas, o du šviesos diodai dešinėje pusėje rodo išėjimus.Rezistoriai, naudojami grandinėje, yra visi 2,2k omų.Kai įjungta A ir B įvesties, o įjungimas išjungtas, išvestis rodo dvejetainę vertę 10, vaizduojančią 2 sumą (1 + 1 + 0 = 10).„XOR“ vartai, pastatyti su pirmaisiais 12 tranzistorių, tvarko pagrindinę sumą, o apatinėje duonos lentos pusėje yra ir arba vartai, skirti nešiotis, spalvotas laidų pavidalas padidina aiškumą ir trikčių šalinimą.

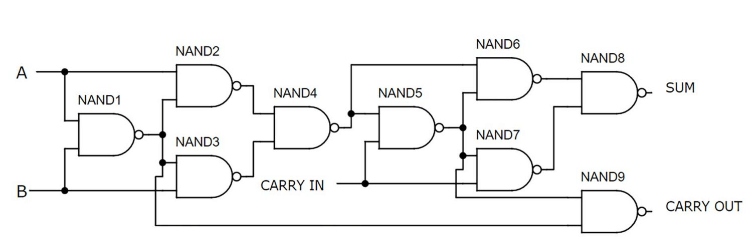

Visas papildymas naudojant „Nand Gates“

7 paveikslas: Visas papildymas naudojant „NAND Gates“

Šis visas papildymas naudoja devynis NAND vartus, kurių vartai yra pagaminti iš dviejų tranzistorių, iš viso 18 tranzistorių.Šis metodas yra vienas paprasčiausių ir efektyviausių būdų, kaip sukurti visą papildymą, naudojant atskiras komponentus.Visi vartai yra surinkti viršutinėje duonos lentos pusėje, o jungikliai užima apatinę pusę.Grandinės funkcionalumas parodomas naudojant A ir B įvestis ir įjungimo įjungimą, todėl išėjimo dvejetainė vertė yra 10, lygi dešimtainei 2 d.

Visas papildymas su nei vartais

8 paveikslas: Visas priedas su nei vartais

Sukurtas su devyniais ir vartais, kiekvienam, kuriam reikia dviejų tranzistorių, šioje sąrankoje iš viso taip pat naudojami 18 tranzistorių.Visas papildymas su „NOR Gates“ siūlo gerą alternatyvą, tačiau apima sudėtingesnius laidus, palyginti su NAND vartais.Kiekvienas tranzistorius NOR vartuose yra įžemintas, o kolekcininkai sujungti oranžinių megztinių laidais, kad būtų užtikrintas tvarkingas ir organizuotas laidus.Ši konfigūracija parodyta su aktyvuotomis įvestimis A ir B bei išjungta įnešimą, todėl išėjimai, kuriuose yra aktyvus, ir suma yra išjungta.

Atliekant šį „Basic Technology“ tyrinėjimą, pradedant nuo pagrindinių pusės priedų iki modernių pilnų papildomųjų dizainų, akivaizdu, kad šie komponentai yra pagrindiniai skaitmeninės elektronikos tobulinimo pagrindai.Operacinės charakteristikos ir įgyvendinimo pavyzdžiai pateikė pabrėžiamą priedų universalumą ir efektyvumą įvairiose skaičiavimo sąlygose.Išnagrinėdami priedų struktūrą ir funkcijas, ypač per jų tiesos lenteles ir būdingas lygtis, mes įgyjame vertingų įžvalgų apie jų galimybes ir apribojimus.Šios žinios padeda tobulinti efektyvesnes ir greitesnes skaičiavimo sistemas.Galiausiai priedai ne tik supaprastina sudėtingus dvejetainius skaičiavimus, bet ir suteikia galimybę daugintis technologijos tokiose įvairiose srityse kaip duomenų apdorojimas, atminties paskirstymas ir skaitmeninio signalo apdorojimas.Tobulėjant skaitmeninėms technologijoms, nuolatinis tobulinimas ir naujovės „BroDDER“ dizaine ir toliau bus kertinis akmuo kuriant pažangesnes skaičiavimo architektūras, užtikrinant, kad šie pagrindiniai komponentai išliks skaitmeninės sistemos projektavimo ir įgyvendinimo pagrindas.

Dažnai užduodami klausimai [DUK]

1. Kas yra visa priedo grandinė?

Visas priedas yra skaitmeninė grandinė, pridedanti tris dvejetainius bitus, kad gautų sumą ir nešiojamąjį išėjimą.Jis skirtas pridėti tris įvestis: du reikšmingus bitus ir vieną nešiojimo bitą iš ankstesnio papildymo.Tai leidžia jį naudoti iš eilės, norint pridėti kelių bitų dvejetainius skaičius.

2. Kiek ir, arba, „XOR“, pilnai pridedamas?

Tipiškame pilname priede yra:

Du xor vartai už sumą.

Du ir vartai prisideda prie atlikimo skaičiavimo.

Vienas ar vartai, skirti baigti išvestį.

3. Kas yra „Carry“ įvestis visu papildymu?

„Carry“ įvestis (CIN) pilname papildyme yra nešiojimo bitas, pridedant ankstesnius mažesnius reikšmingus bitus, susijusius su dvejetainiu dvejetainiu papildymu.Skaičiuojant dabartinę sumą ir naująjį perkėlimą, tai leidžia apsvarstyti šį ankstesnį nešiojimą.

4. Kodėl verta naudoti visą papildymą, o ne pusmetį?

Vietoj pusės papildymo naudojamas visas priedas, nes jis gali pridėti tris bitus (įskaitant nešiojimą iš ankstesnių papildymų), todėl jis tinka sujungti kartu, kad būtų galima pridėti kelių bitų skaičius.Pusėangė gali pridėti tik du bitus ir neturi nuostatos dėl perkėlimo, o tai riboja jo naudojimą iki paprasčiausių dvejetainių papildymo formų be nuoseklaus nešiojimo sklidimo.

Dalintis: