EP1C4F324C7N FPGA: duomenų lapas, funkcijos, programavimas ir specifikacijos

Šis vadovas yra susijęs su EP1C4F324C7N, „Intel“ pagaminto FPGA lusto tipu.Tai puikiai tinka projektams, kuriems reikalingi stiprūs rezultatai, tačiau taip pat reikia likti neviršijant biudžeto.Šiame straipsnyje sužinosite, ką gali padaryti ši lusis, kaip ji veikia, kur ji naudojama ir kaip ją užprogramuoti.Nesvarbu, ar dirbate prie automobilių, gamyklų ar net namų įrenginių elektronikos, šis vadovas padės suprasti, kodėl EP1C4F324C7N yra protingas ir lankstus pasirinkimas.Katalogas

EP1C4F324C7N apžvalga

EP1C4F324C7N yra „Intel“ „Cyclone® FPGA“ serijos dalis, specialiai sukurta ekonomiškai efektyvioms programoms, reikalaujančioms gero našumo ir mažų išlaidų balanso.Šioje FPGA turi 4000 loginių elementų ir 400 loginio masyvo blokų (laboratorijos), suteikiančios patikimas galimybes vidutinio sunkumo sudėtingumo dizainui.Tai apima 76,5 kilobitų bendros RAM ir palaiko iki 249 I/O kaiščius, todėl jis yra labai universalus dėl įvairių sąsajų reikalavimų.EP1C4F324C7N, veikiantis iki 320 MHz dažniais iki 320 MHz ir turinčios tiekimo įtampos diapazoną nuo 1,425 V iki 1,575 V, yra įrengtas reikalaujančioms programoms tvarkyti.Jis palaiko platų I/O standartų asortimentą, tokius kaip LVTTL, LVCMOS, SSTL-2 ir SSTL-3, ir yra suderinamas su išorinių atminties tipais, tokiais kaip DDR SDRAM, padidindamas savo naudingumą skaitmeninio signalo apdorojimo, įterptųjų skaičiavimo ir automatizavimo sistemose.

Jei norite, kad jūsų operacijos vyktų sklandžiai naudodamiesi patikimomis technologijomis, pateikdami didelę šios FPGA užsakymą su mumis, galite padėti įsitikinti, kad turite jūsų projektų prieinamumą ir nuoseklumą.

EP1C4F324C7N CAD modeliai

EP1C4F324C7N simbolis

EP1C4F324C7N pėdsakai

EP1C4F324C7N 3D modelis

EP1C4F324C7N funkcijos

• Loginiai elementai: FPGA yra 4000 loginių elementų, leidžiančių efektyviai įgyvendinti sudėtingas logines grandines ir skaitmenines funkcijas.

• Logikos masyvo blokai (laboratorijos): Tai apima 400 laboratorijų, kurios yra pagrindiniai FPGA architektūros elementai, palengvinančios universalių skaitmeninių loginių konfigūracijų dizainą.

• Iš viso RAM bitai: „FPGA“ yra su 76,5 kilobitais įterptosios RAM, teikiančios lusto atminties išteklius greitųjų duomenų apdorojimui ir saugojimui.

• I/O kaiščių skaičius: Naudodamas 249 vartotojo sukonfigūruotus I/O kaiščius, EP1C4F324C7N palaiko daugybę sąsajų parinkčių, pritaikomų įvairiems signalo standartams ir elektroniniams komponentams.

• Veikimo dažnis: Jis gali veikti dažniais iki 320 MHz dažniu, leisdamas jam efektyviai atlikti greitųjų skaičiavimo užduotis ir procesus.

• Tiekimo įtampa: Įrenginys veikia tiekimo įtampos diapazone nuo 1,425 V iki 1,575 V, užtikrinant lanksčią ir patikimą galios valdymą įvairiose programose.

• Fazės užrakintos kilpos (PLLS): Jame yra fazių užrakintos kilpos, skirtos tiksliam laikrodžio valdymui, kad būtų galima pritaikyti laiką.

• Palaikymas keliems I/O standartams: FPGA palaiko įvairius I/O standartus, tokius kaip LVTTL, LVCMOS, SSTL-2 ir SSTL-3, kurie padidina jo suderinamumą su plačiu elektroninių komponentų ir sistemų asortimentu.

EP1C4F324C7N BLOCK diagrama

Diagrama iliustruoja sujungimo struktūrą FPGA, konkrečiai nurodant EP1C4F324C7N Įrenginys iš „Altera Cyclone“ serijos.Šio išdėstymo esmė yra Logikos masyvo blokai (Laboratorijos), kurios yra vertikaliai suderinti moduliai, kuriuose yra loginių elementų klasteriai, atsakingi už vartotojo loginių funkcijų įgyvendinimą.Kiekviena laboratorija yra sujungta su kaimyninėmis laboratorijomis per tiesioginius ryšius sujungimais, leidžiančiais užmegzti greitą ryšį ir sumažinti signalo sklidimo vėlavimą.Šios tiesioginės nuorodos suteikia efektyvų, lokalizuotą duomenų perdavimą tarp gretimų loginių blokų, nenaudojant platesnių maršruto parinkimo išteklių.

Aplink laboratorijas yra du pagrindiniai globalių jungčių tipai: eilutės sujungimai ir stulpelių sujungimai.Šios plačios mėlynos linijos yra maršrutizavimo greitkeliai, leidžiantys signalams pereiti per didesnes FPGA audinio dalis.Eilutės sujungimai veikia horizontaliai, o kolonėlės sujungtos vertikaliai veikia.Jie palengvina ryšį tarp tolimų loginių blokų ir sąsajos su įvesties/išvesties elementais ar kitais funkciniais vienetais, esančiais per lustą.

Vietinis sujungimas yra tarp laboratorijų ir yra perjungimo audinys, kuris sujungia pasaulinius ryšius su laboratorijomis.Tai leidžia loginiams blokams pasiekti signalus tiek iš tiesioginių, tiek iš pasaulinių sujungimų.Ši maršruto parinkimo hierarchija, derinanti tiesioginį, vietinį, eilutės ir stulpelio kelius, suteikia lankstų ir keičiamą požiūrį į signalo pasiskirstymą, optimizuodamas našumo ir logikos panaudojimą EP1C4F324C7N FPGA.

EP1C4F324C7N specifikacijos

|

Tipas |

Parametras |

|

Gamintojas |

Altera/intel |

|

Serija |

Cyclone® |

|

Pakuotė |

Dėklas |

|

Dalies būsena |

Pasenęs |

|

Laboratorijų/CLB skaičius |

400 |

|

Loginių elementų/ląstelių skaičius |

4000 |

|

Iš viso RAM bitai |

78,336 |

|

I/O skaičius |

249 |

|

Įtampa - tiekimas |

1,425 V ~ 1,575 V |

|

Montavimo tipas |

Paviršiaus laikiklis |

|

Darbinė temperatūra |

0 ° C ~ 85 ° C (TJ) |

|

Paketas / atvejis |

324-BGA |

|

Tiekėjo įrenginių paketas |

324-FBGA (19x19) |

|

Bazinis produkto numeris |

EP1C4 |

EP1C4F324C7N programos

Tinklo įranga

EP1C4F324C7N yra labai tinkamas naudoti tinklų kūrimo įrenginiuose, tokiuose kaip jungikliai, maršrutizatoriai ir modemai.Tai padeda efektyviai valdyti duomenų srautą, gerinant pralaidumą ir sumažinant delsos, kad būtų galima išlaikyti aukštos kokybės tinklo operacijas.

Pramoninė automatika

Pramonės automatizavimo srityje ši FPGA gali būti naudojama mašinų ir robotų sistemoms valdyti.Jos gebėjimas apdoroti sudėtingus algoritmus greitai leidžia kontroliuoti ir stebėti, padidina produktyvumą ir saugą gamybos aplinkoje.

Vartojimo elektronika

„EP1C4F324C7N“ randa programas vartojimo elektronikoje, ypač vairuojant didelės skiriamosios gebos ekranus ir valdant interaktyvias sąsajas tokiuose įrenginiuose kaip „Smart TV“ ir „Advanced Home Automation Systems“.Tvirtos jo apdorojimo galimybės užtikrina sklandų ir reaguojančią patirtį.

Automobilių sistemos

Automobilių programose ši FPGA prisideda prie pažangių vairuotojų ir pagalbinių sistemų (ADAS) ir transporto priemonių ir pramogų informacinių sistemų funkcionalumo.Tai remia apdorojimo ir sprendimų priėmimą dėl saugos ir pramogų ypatybių šiuolaikinėse transporto priemonėse.

Aviacijos ir kosmoso ir gynybos

FPGA taip pat taikoma aviacijos ir kosmoso ir gynybos sektoriuose, kur ji tvarko signalo ir vaizdo apdorojimo užduotis radaro ir ryšių sistemoms.Dėl didelio patikimumo ir gebėjimo veikti ekstremaliomis sąlygomis jis yra idealus karinėms ir kosmoso programoms.

EP1C4F324C7N Panašios dalys

EP1C4F324C7N programavimo veiksmai

1. Dizaino kūrimas: Pradėkite rašydami savo dizainą naudodami aparatinės įrangos aprašymo kalbą, tokią kaip VHDL ar „Verilog“.Šis kodas apibūdina jūsų aparatinės įrangos diegimo loginę struktūrą ir funkcijas.Svarbu tiksliai išversti savo aparatūros idėją į DTL, kad būtų užtikrinta, jog FPGA elgiasi taip, kaip tikėtasi.Prieš pradėdami diegti aparatinę įrangą, modeliuokite savo DTL kodą naudodamiesi modeliavimo programine įranga.Šis žingsnis patikrina jūsų dizaino logiką ir funkcionalumą virtualioje aplinkoje, leidžiant jums nustatyti ir ištaisyti klaidas kūrimo proceso pradžioje.

2. Kompiliacija ir sintezė : Norėdami sudaryti ir sintetinti savo DTL kodą, naudokite „Altera“ „Quartus II“ programinę įrangą.Kompiliacija paverčia jūsų DTL į tinklą, bendrą FPGA aparatinės įrangos, kuri jūsų dizainą susieja su loginiais elementais ir nukreipimo ištekliais, aprašymą.Tinkamumo procesas, „Quartus II“ darbo eiga, apima savo dizaino įdėjimą ir nukreipimą į FPGA.Tai optimizuoja loginių elementų išdėstymą ir jungčių maršrutą, kad atitiktų našumo reikalavimus ir sumažintų išteklių naudojimą.

3. PIN paskirstymas: PIN planuotojas II kvarteze leidžia jums priskirti konkrečius FPGA kaiščius į įvestis ir išvestis, apibrėžtomis jūsų DTL kode.Tinkamas PIN priskyrimas yra tinkamas fiziniam FPGA ryšiui ir sąveikai su kitais jūsų sistemos aparatūros komponentais.

4. Laiko analizė: Norėdami įsitikinti, kad jūsų dizainas atitinka laiko nustatymo reikalavimus, naudokite „TimeQuest“ laiko analizatorių.Šis įrankis patikrina sąrankos ir laikymo laiką bei bendrą laiko nustatymo našumą, padedantį užkirsti kelią tokioms problemoms kaip duomenų sugadinimas ir sistemos nestabilumas.

5. Programavimo failų generavimas: Po to, kai dizainas bus sudarytas, sintetinamas ir patikrintas pagal laiką, naudokite „Quartus II“ surinkėjo įrankį, kad sugeneruotumėte programavimo failą.Šis failas, paprastai su .SOF (SRAM objekto faile) arba .pof (programuojamo objekto failo) plėtinyje, yra FPGA konfigūracijos duomenys.

6. Įrenginio programavimas: Prijunkite FPGA plokštę prie savo kompiuterio naudodami JTAG sąsają, tokią kaip USB-Blaster.Ši sąsaja naudojama programavimo failo perkėlimui iš kompiuterio į FPGA.Atidarykite „Quartus II“ programuotojo įrankį, kad įkeltumėte ir perkeltumėte programavimo failą į FPGA.Šis žingsnis sukonfigūruoja FPGA savo dizainu, iš esmės „programuojant“ įrenginį norimoms funkcijoms atlikti.

7. Patikrinimas: Kai FPGA bus užprogramuota, atlikite funkcinius bandymus, kad patikrintumėte, ar FPGA veikia teisingai pagal projektavimo specifikacijas.Šis bandymas gali apimti bandymo atvejų vykdymą laboratorijos aplinkoje, sąsajos operacijų patikrinimą ir užtikrinimą, kad FPGA teisingai sąveikauja su kitais aparatinės įrangos komponentais.

EP1C4F324C7N pranašumai

Lankstumas ir pertvarkymas

„EP1C4F324C7N“ siūlo neprilygstamą lankstumą, palyginti su mikrovaldikliais ir ASIC, kurie yra fiksuojami jų funkcijoje.Šią FPGA gali būti perprogramuota, kad būtų galima prisitaikyti prie naujų reikalavimų ar sistemos projektavimo pokyčių, kurie laikui bėgant vystosi.Šis pertvarkingumas leidžia atnaujinti savo sistemas nepakeičiant aparatinės įrangos, sutrumpinant sąnaudų ir kūrimo laiką.

Lygiagrečios apdorojimo galimybės

Turėdamas galimybę vienu metu vykdyti kelias operacijas, EP1C4F324C7N išsiskiria aplinkoje, kuriai reikalingas aukštos kokybės skaičiavimas.Ši lygiagretus apdorojimo galimybes yra pranašumas prieš tradicinius mikrovaldiklius, kurie veikia nuosekliai, todėl FPGA yra tinkamesnis intensyviam programoms, tokioms kaip skaitmeninio signalo apdorojimas, vaizdo įrašų apdorojimas ir sudėtingos valdymo sistemos.

Pasirinktinė aparatinės įrangos įgyvendinimas

FPGA leidžia projektuoti pasirinktinę aparatūros logiką, pritaikytą specialiai vartotojo veikimo poreikiams.Tai reiškia, kad EP1C4F324C7N gali būti optimizuotas efektyviau atlikti specifines užduotis nei standartiniai procesoriai ar ASIC, užtikrinant puikų našumo ir energijos efektyvumą specializuotoms programoms.

Ekonominis efektyvumas gaminant nuo mažo iki vidutinio tūrio

Projektams, kuriuose gamybos apimtys nepateisina didelių ASIC kūrimo išlaidų, EP1C4F324C7N yra ekonomiškai efektyvi alternatyva.Tai suteikia pritaikytos aparatinės įrangos pranašumus be didelių išankstinių investicijų, reikalingų ASIC projektavimui ir gamybai, todėl ji yra ideali prototipams, mažiems ir vidutiniams projektams ar specializuotoms pramonės programoms.

Integracija ir erdvės efektyvumas

Gebėjimas integruoti kelias funkcijas ir komponentus į vieną FPGA lustą daro EP1C4F324C7N labai vertingą erdvėje suvaržytose programose.Ši integracija lemia mažesnius, kompaktiškesnius įrenginių dizainus, puikų nešiojamoje elektronikoje, automobilių programose ir kitose scenarijuose, kuriuose reikalingas erdvės efektyvumas.

EP1C4F324C7N pakavimo matmenys

• Paketo tipas: 324 kontaktų smulkaus kamuolio tinklelio masyvas (FBGA)

• Pakuotės dydis (Ilgis x plotis): 19 mm x 19 mm

• Maksimalus sėdintis aukštis: 3,5 mm

• Terminalo žingsnis: 1 mm

EP1C4F324C7N gamintojas

EP1C4F324C7N yra lauko programuojama vartų masyvas (FPGA), pagamintas pagal „Intel“, įsigiję Alterą.Kaip „Intel's Cyclone®“ serijos dalis, ši FPGA yra plačiojo „Intel“ integruotų technologijų sprendimų portfelio segmentas.„Intel“, puslaidininkių pramonės lyderis, integruoja pažangias gamybos technologijas ir didelę paramą, kad būtų užtikrinta patikimi FPGA sprendimai, įskaitant EP1C4F324C7N, kuriame yra sudėtingos loginės galimybės kompaktiškos formos faktoriuje.Ši FPGA pabrėžia „Intel“ įsipareigojimą pristatyti aukštos kokybės skaičiavimo komponentus, kurie patenkintų įvairius technologinius poreikius.

Išvada

Nesvarbu, ar kuriate pasirinktinę valdymo logiką, kurdami greitųjų ryšių sistemas, ar prototipų kūrimą specializuotos skaitmeninės funkcijos, „EP1C4F324C7N FPGA“ suteikia optimalų našumo, lankstumo ir išlaidų balansą.Dėl savo plačiojo I/O suderinamumo, integruotos atminties ir efektyvaus pertvarkymo jis palaiko keičiamą ir efektyvų erdvę turinčią dizainą įvairiose šiuolaikinėse programose.Ši FPGA, remiama „Intel“ pramonėje pirmaujančia parama, išlieka patikimu ir pritaikomu sprendimu siekiant patikimos programuojamos logikos tiek mažos, tiek vidutinės apimties diegimo metu.

Duomenų lapas PDF

EP1C4F324C7N duomenų lapai:

Visi „Dev Pkg CHG 1“/2018 m. Rugpjūtis

Mult Desicant CHG 19/liepa/2019.pdf

„Mult Series“ programinė įranga CHGS 26/kovo/2020.pdf

Virtualus JTAG megafuntion vadovas.pdf

Cilindrinės akumuliatorių laikikliai.pdf

„Mult Dev“ substrato medžiaga CHG 25/2017 m. Rugpjūčio mėn. PDF

Apie mus

ALLELCO LIMITED

Skaityti daugiau

Greitas užklausa

Prašau atsiųsti užklausą, mes nedelsdami atsakysime.

Dažnai užduodami klausimai [FAQ]

1. Ar „Ep1c4f324c7n“ galima naudoti su DDR arba SDRAM?

Taip, ši FPGA palaiko išorinių atminties tipus, įskaitant DDR SDRAM, dėka savo daugiašalės I/O palaikymo.Tačiau jūsų PCB išdėstymas turi laikytis griežtų laiko nustatymo ir varžos gairių, susijusių su greitųjų atminties sąsajomis.

2. Kokie yra tipiniai EP1C4F324C7N galios reikalavimai?

Šis prietaisas veikia nuo 1,425 V iki 1,575 V šerdies įtampos, o I/O standartams reikalinga papildoma įtampa.Norėdami tiksliai planuoti energijos planavimą, naudokite „Intel“ „PowerPlay Power“ analizatorių „Quartus“, kad įvertintumėte vartojimą pagal savo dizainą.

3. Ar EP1C4F324C7N ROHS yra suderinami ir be švino?

Taip, EP1C4F324C7N atitinka ROHS direktyvas ir yra prieinamas be švino paketų.Dėl to jis tinka aplinkai reguliuojamoms rinkoms ir programoms, kurioms reikalingas žaliosios elektronikos sertifikavimas.

4. Kiek laiko reikia sudaryti ir užprogramuoti dizainą į EP1C4F324C7N?

Vidutinio sudėtingumo dizainui, kompiliavimas ir programavimas paprastai trunka nuo 3 iki 5 minučių, atsižvelgiant į jūsų kompiuterio našumą.Laiko analizė ir kaiščių priskyrimai gali išplėsti procesą, jei jūsų dizainui reikia griežtų laiko apribojimų.

5. Ar man reikia kokių nors specialių įrankių, kad būtų galima programuoti EP1C4F324C7N?

Jums reikės „Intel“ „Quartus II“ programinės įrangos, kurią galima įsigyti nemokamame „Lite Edition“ ir „USB-Blaster“ ar suderinamą JTAG programuotoją.Šie įrankiai leidžia sudaryti savo dizainą, generuoti programavimo failus ir įkelti juos į FPGA.

GC5330IZEV Skaitmeninio signalo procesorius: funkcijos, programos, alternatyvos ir specifikacijos

2025/04/1

Išsamus 0402 rezistoriaus vadovas: specifikacijos, programos ir litavimo būdai

2025/04/1

Populiarūs įrašai

-

Sudėtingos instrukcijos Nustatykite kompiuterius: kaip jie pakeitė skaičiavimą?

8000/04/18 147778

-

USB-C PINOUT ir funkcijos

2000/04/18 112027

-

„Xilinx Unified“ modeliavimo primityvų naudojimas: išsamus FPGA projektavimo ir modeliavimo vadovas

1600/04/18 111351

-

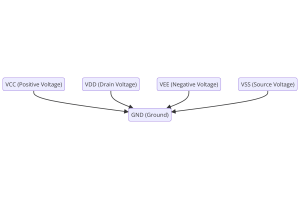

Maitinimo įtampa elektronikoje: VCC, VDD, VEE, VSS ir GND reikšmė

0400/04/18 83780

-

„RJ45“ jungties vadovas: „Pmout“, laidų, laidų tipai ir naudojimas

1970/01/1 79578

-

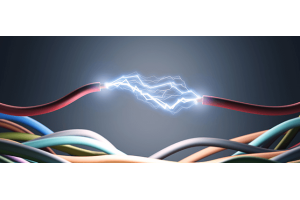

Pagrindinis vielos spalvų kodų vadovas šiuolaikinėse elektrinėse sistemose

Tai, kaip mūsų elektros sistemos naudoja spalvas, nėra tik išvaizdos.Kiekviena vielos spalva dabar rodo konkrečią funkciją, todėl montavimo ir priežiūros metu lengviau nustatyti ir tvarkyti elektro...1970/01/1 66971

-

Išvalymo vožtuvo vadovas: funkcija, simptomai, testavimas ir pakeitimas, kad būtų galima optimaliai atlikti variklio veikimą

Išvalymo vožtuvas yra pagrindinė automobilio sistemos dalis, padedanti išlaikyti orą švarų, valdant degalų garus, kol jie gali ištrūkti į atmosferą.Tai ne tik padeda aplinkai sumažinti taršą, bet i...1970/01/1 63107

-

Kokybės (Q) faktorius: lygtys ir programos

Kokybės koeficientas, arba „Q“, yra svarbus tikrinant, kaip gerai induktoriai ir rezonatoriai veikia elektroninėse sistemose, kuriose naudojami radijo dažniai (RF).„Q“ matuoja, kaip gerai grandinė ...1970/01/1 63041

-

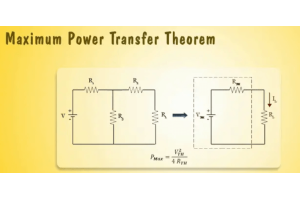

Pasiekti maksimalų našumą naudojant maksimalios galios perdavimo teoremą

Maksimalios galios perdavimo teorema paaiškina, kaip energija iš šaltinio, pavyzdžiui, akumuliatorius ar generatorius, teka į prijungtą apkrovą.Tai parodo tikslią sąlygą, kai apkrova gauna daugiaus...1970/01/1 54097

-

A23 akumuliatoriaus specifikacijos ir suderinamumas

„A23“ baterija yra maža, cilindro formos akumuliatorius, turintis aukštą įtampą.Taip pat vadinamas 23A, 23AE arba MN21, jis veikia esant 12 voltų ir daug aukštesnis nei AA ar AAA baterijos...1970/01/1 52191