EP20K100EFC324-1X FPGA: funkcijos, specifikacijos, programos ir programavimo vadovas

„EP20K100EFC324-1X“ yra programuojamas lustas (FPGA) iš „Intel's Altera Apex-20ke®“ serijos.Jis skirtas tvarkyti sudėtingas skaitmenines grandines ir palaiko spartų duomenų apdorojimą.Šis vadovas paaiškina jo ypatybes, specifikacijas, kaip ją užprogramuoti ir jo pranašumus, todėl tai yra naudingas šaltinis visiems.Katalogas

EP20K100EFC324-1X apžvalga

EP20K100EFC324-1X yra „Intel“ „Altera Apex-20ke®“ serijos, lauko programuojamo vartų masyvo (FPGA), pritaikytos didelio tankio programuojamoms loginėms programoms, dalis, kurios reikalauja modernių sistemų, programuojamų mikroschemų (SOPC) integracijose.Šis įrenginys išsiskiria iš jo integracijos 4 160 loginių elementų arba langelių ir 416 loginio masyvo blokų (laboratorijos), kurie palengvina esminį įvairių skaitmeninių grandinių dizainų konfigūravimą.Tai taip pat gali pasigirti nemaža dalis įterptos atminties, kuriai priklauso reikalaujantys duomenų saugojimo reikalavimų FPGA.Toliau padidindamas savo taikymo universalumą, „EP20K100EFC324-1X“ palaiko 246 I/O kaiščius ir siūlo didelį maždaug 263 000 ekvivalentų vartų vartų skaičių, efektyviai veikia nuo 1,71 V iki 1,89 V.Jis yra supakuotas į 324 rutulio smulkiojo rutulinio tinklelio masyvą (FBGA), kuris padeda tvirtai fiziškai integruoti į elektroninius mazgus.

„EP20K100EFC324-1X“ yra puikus pasirinkimas, kai esate pasirengęs su mumis pateikti didelius užsakymus savo projektams ar produktų linijoms.

EP20K100EFC324-1X CAD modeliai

EP20K100EFC324-1X simbolis

EP20K100EFC324-1X pėdsakas

EP20K100EFC324-1X 3D modelis

EP20K100EFC324-1X funkcijos

• Didelis loginis tankis: FPGA yra aprūpinti 4 160 loginių elementų (LES) ir 416 loginio masyvo blokų (laboratorijos).Šis didelis loginių ląstelių tankis leidžia suprojektuoti ir vykdyti sudėtingas skaitmenines grandines ir sistemas viename luste, todėl jis yra idealus programoms, reikalaujančioms patikimų loginio apdorojimo galimybių.

• Įterpta atmintis: Siūlydamas 53 248 RAM bitus, šis FPGA suteikia didelius įterptus atminties išteklius.Ši funkcija tinka programoms, kurioms reikalingas greitas duomenų saugojimas ir gavimas, leidžianti efektyviai tvarkyti daug duomenų reikalaujančių užduočių.

• Plačios I/O galimybės: Naudodami 246 įvesties/išvesties kaiščius, EP20K100EFC324-1X užtikrina išsamias ryšio ir sąsajos parinktis.Šis platus I/O galimybių asortimentas leidžia lengvai susisiekti su daugybe išorinių įrenginių ir sistemų, padidindama jo naudingumą sudėtinguose elektroniniuose mazguose.

• Kelių įtampos palaikymas: Įrenginys palaiko pagrindinio įtampos diapazoną nuo 1,71 V iki 1,89 V ir turi „MultiVolt ™ I/O“ sąsają.Tai leidžia FPGA būti suderinami su kitais elektroniniais komponentais, veikiančiais įvairiais loginiu lygmenimis, įskaitant 1,8 V, 2,5 V, 3,3 V ir 5,0 V, užtikrinančias didelį lankstumą sistemos projektavimui.

EP20K100EFC324-1X BLOCK DIAGRAMA

EP20K100EFC324-1X BLOCK DIAGRAMA Atspindi vidinę FPGA (lauko programuojamų vartų masyvo) įrenginio struktūrą, parodantį įvairius jo funkcinius blokus.Diagramą sudaro sujungti loginiai blokai, atminties elementai, laikrodžio valdymas ir I/O elementai.Dizaino esmė yra Logikos masyvo blokai (Laboratorijos), kuriose yra Pažvelgimo lentelės (LUT) ir produkto terminuotos logika.Šie elementai leidžia įdiegti lankstų logiką, todėl FPGA yra tinkamas greitųjų valdymo logikai, būsenos mašinoms ir DSP funkcijoms. „FastTrack“ sujungimas Suteikia greitą ryšio kelią tarp loginių elementų, užtikrinant efektyvų signalo maršrutą visame įrenginyje. Laikrodžio valdymo grandinės , įskaitant „Clocklock“ funkciją, užtikrina patikimą ir sinchronizuotą veikimą stabilizuodamas ir paskirstant laikrodžio signalus visame FPGA. Įvesties/išvesties elementai (IOES), išdėstyta aplink FPGA audinį, tarnauja kaip išorinio ryšio sąsajos.Šie IOE palaiko kelis pramonės standartinius protokolus, tokius kaip PCIAr GTL+Ar SSTL-3, ir LVD, įgalinant FPGA sąsają su įvairiomis išorinėmis sistemomis.Šie IOE užtikrina suderinamumą su skirtingais įtampos lygiais ir signalizacijos standartais, padidindami FPGA universalumą įterptomis programomis. Įterpti atminties blokai Pateikite lanksčius saugojimo sprendimus FPGA.Šie atminties elementai gali veikti kaip Turinio adresuojama atmintis (CAM), Atsitiktinės prieigos atmintis (Ram), Tik skaitoma atmintis (ROM), Pirma pirmiausia (FIFO) buferiai ir kitos atminties struktūros.Gebėjimas tiesiogiai integruoti atmintį tiesiogiai FPGA audinyje pagerina duomenų apdorojimo efektyvumą, sumažinant išorinės atminties priklausomybes ir latenciją.

EP20K100EFC324-1X specifikacijos

|

Tipas |

Parametras |

|

Gamintojas |

„Intel“ |

|

Serija |

„Apex-20ke®“ |

|

Pakuotė |

Dėklas |

|

Dalies būsena |

Pasenęs |

|

Laboratorijų/CLB skaičius |

416 |

|

Loginių elementų/ląstelių skaičius |

4160 |

|

Iš viso RAM bitai |

53248 |

|

I/O skaičius |

246 |

|

Vartų skaičius |

263000 |

|

Įtampa - tiekimas |

1,71V ~ 1,89 V. |

|

Montavimo tipas |

Paviršiaus laikiklis |

|

Darbinė temperatūra |

0 ° C ~ 85 ° C (TJ) |

|

Paketas / atvejis |

324-BGA |

|

Tiekėjo įrenginių paketas |

324-FBGA (19x19) |

|

Bazinis produkto numeris |

EP20K100 |

EP20K100EFC324-1X programos

Tinklų kūrimas ir ryšiai

Ši FPGA yra ideali tinklų kūrimo įrangai, tokioms kaip maršrutizatoriai ir jungikliai, kur ji tvarko duomenų maršrutą, signalo apdorojimą ir protokolo tvarkymą.Didelis loginis tankis ir plačios I/O galimybės leidžia jai palaikyti sudėtingas, greitas duomenų operacijas, reikalingas šiuolaikinėje ryšių infrastruktūroje.

Pramoninės kontrolės sistemos

Pramonės sektoriuje EP20K100EFC324-1X išsiskiria automatizavimo sistemomis.Jos programavimo ir patikimos apdorojimo galimybės leidžia tiksliai valdyti ir stebėti, kaip padidinti veiklos efektyvumą ir patikimumą gamybos procesuose.

Automobilių elektronika

FPGA yra automobilių programų komponentas, ypač pažengusiose vairuotojų ir pagalbinių sistemose (ADAS) ir transporto priemonių pramogų ir pramogų sistemose.Tai suteikia reikalingą apdorojimo galią ir pritaikomumą duomenims tvarkyti ir palaikyti modernias modernias transporto priemones reikalingas sudėtingas funkcijas.

Vartojimo elektronika

Dėl savo lankstumo ir aukšto našumo „EP20K100EFC324-1X“ taip pat randamas vartojimo elektronikoje, tokiose kaip aukštos raiškos televizoriai ir žaidimų konsolės.Tai palaiko sudėtingas funkcijas ir padeda sutrumpinti produktų kūrimo ciklus, tenkinančias greitą vartojimo elektronikos rinkos paklausą.

Medicinos prietaisai

Medicinos srityje ši FPGA prisideda prie medicininės vaizdo gavimo įrangos ir diagnostinių priemonių funkcionalumo.Jos gebėjimas apdoroti duomenis dideliu greičiu užtikrina, kad šie prietaisai gali pateikti tikslius ir laiku diagnozuotus veiksmingo gydymo ir vaizdavimo diagnostinius rezultatus.

EP20K100EFC324-1X Panašios dalys

EP20K100EFC324-1X Programavimo veiksmai

Norėdami veiksmingai užprogramuoti EP20K100EFC324-1X, „Altera“ „Apex-20ke® FPGA“ serijos narį, svarbu sekti struktūrizuotą žingsnių seką.Šis procesas užtikrina, kad jūsų dizainas būtų efektyviai išverstas į formatą, kurį FPGA gali vykdyti.Žemiau aprašau išsamų šio FPGA modelio programavimo metodą, integruojant veiksmus ir modifikacijas, būdingus šiam įrenginiui.

1. Dizaino įrašas

Pradėkite kurdami savo skaitmeninės logikos dizainą.Naudokite aparatinės įrangos aprašymo kalbas (HDLS), tokias kaip VHDL ar „Verilog“, kurios leidžia apibūdinti jūsų sistemos aparatinės įrangos funkciją ir logiką.Tokie įrankiai kaip „Altera's Quartus II“ siūlo išsamią aplinką rašyti, testuoti ir sudaryti jūsų DTL kodą.Įsitikinkite, kad jūsų dizainas yra modulinis, todėl lengviau derinti ir mastelį.

2. Sintezė

Kai jūsų dizaino įrašas bus baigtas, kitas žingsnis yra sintezė, kai DTL kodas išverstas į tinklą.Šis tinklo sąrašas atspindi sujungtą vartų, „Flip-Flops“ ir kitų aparatūros elementų, sudarančių jūsų dizainą, sąrašą.Sintezės metu kodas yra optimizuotas konkrečiai EP20K100EFC324-1X architektūrai, užtikrinant, kad dizainas efektyviai panaudotų FPGA išteklius.Šiam tikslui gali būti naudojami tokie įrankiai kaip „Synplify Pro“ arba sintezės įrankis „Quartus II“.Svarbu sutelkti dėmesį į savo dizaino optimizavimą, kad būtų galima atitikti laiko ir išteklių apribojimus.

3. Įgyvendinimas

Po sintezės vyksta įgyvendinimas.Šis žingsnis apima tinklo sąrašo žemėlapį į tikrąją FPGA aparatinę įrangą.Tai apima loginių elementų išdėstymą FPGA ir jungčių tarp jų nukreipimą.„Quartus II“ programinė įranga palengvina šį procesą naudodama savo diegimo įrankius, kurie valdo išdėstymą ir maršrutą, kad atitiktų norimą laikrodžio greitį ir našumo metriką.Įdiegimo metu gali tekti pakartoti savo dizainą, remiantis atsiliepimais iš laiko analizės įrankių, kad būtų užtikrinta, jog visi veiklos reikalavimai atitiktų.

4. Bitstream generavimas

Po sėkmingo įgyvendinimo, kitas etapas sukuria „Bitstream“.Tai dvejetainis failas, kuris bus įkeltas į FPGA.„Bitstream“ yra sukonfigūruoti kiekvieno programuojamo FPGA elemento sukonfigūruoti duomenys, nustatant įrenginį funkcijoms atlikti pagal jūsų dizainą.„Quartus II“ programinė įranga gali sugeneruoti šį „Bitstream“, kuris tada yra paruoštas atsisiųsti į FPGA.

5. FPGA programavimas

Paskutinis žingsnis yra programuoti FPGA su sugeneruotu „Bitstream“.Tai galima padaryti naudojant aparatūros programuotoją, suderinamą su EP20K100EFC324-1X, pavyzdžiui, „USB Blaster“.Prijunkite programuotoją prie savo kūrimo lentos, kurioje montuojama FPGA, ir naudokite „Quartus II“ programuotojo įrankį, kad „Bitstream“ perkeltumėte į FPGA.Šis žingsnis įkels jūsų dizainą į FPGA ir jis pradės veikti pagal jūsų DTL kodą apibrėžtą logiką.

EP20K100EFC324-1X Privalumai

Aukšta integracija

„EP20K100EFC324-1X“ siūlo aukštas integracijos galimybes dėl didelio loginių elementų skaičiaus ir įterptos atminties.Ši integracija leidžia sustiprinti daugybę funkcijų į vieną įrenginį.Dėl to sistemos gali būti supaprastintos, sumažindamos bendrą komponentų skaičių, reikalingą fizinę erdvę ir galimus elektroninių dizainų gedimų taškus.

Lankstus logikos įgyvendinimas

„EP20K100EFC324-1X“ architektūra palaiko ir „Look-up“ lentelę (LUT), ir produkto terminą pagrįsta logika.Šis logikos diegimo lankstumas leidžia optimizuoti FPGA įvairioms programoms, pradedant paprastais logikos vartais ir baigiant sudėtingomis kombinuotomis grandinėmis.Tai suteikia pranašumą dizaino universalumo srityje ir gali pritaikyti platų skaitmeninių funkcijų spektrą.

Išplėstinė sujungimo struktūra

FPGA, pasižymintis hierarchine sujungimo struktūra, apima „Local“, „Megalab ™“ ir „FastTrack®“ sujungimus.Šie specializuoti maršrutizacijos ištekliai padidina signalo maršruto efektyvumą ir pagerina bendrą įrenginio našumą.Ši patobulinta sujungimo struktūra yra gera dizainui, kuriam reikalingas greitas duomenų perdavimas ir mažas delsos, todėl FPGA yra idealus didelio našumo skaičiavimui ir telekomunikacijoms.

Laikrodžio valdymas

„EP20K100EFC324-1X“ apima „Clocklock“ ir „ClockBoost“ technologiją, kuri padeda efektyviai valdyti laikrodį.Šios savybės padeda išlaikyti laikrodžio signalo vientisumą visame FPGA, mažinant virvę ir pagerinant signalo patikimumą.Efektyvus laikrodžio valdymas reikalingas sinchroninėms skaitmeninėms grandinėms, užtikrinant stabilų ir nuspėjamą veikimą įvairiomis aplinkos sąlygomis.

Dizaino lankstumas

Programuojamas EP20K100EFC324-1X pobūdis leidžia pritaikyti aparatinę įrangą konkrečiems poreikiams ir pertvarkyti FPGA skirtingoms programoms ar atnaujinimams.Šis lankstumas reiškia, kad viena FPGA gali būti naudojama keliuose projektuose, o tai yra naudinga dinaminiame technologinėje aplinkoje, kur reikalavimai gali greitai pasikeisti.

Greitas prototipų kūrimas

FPGA, pavyzdžiui, EP20K100EFC324-1X, įgalina greitą skaitmeninių grandinių prototipų nustatymą.Galite greitai kurti ir pakartoti dizainus be ilgo povandeninių laikų, susijusių su pasirinktine ASIC vystymuisi.Šis gebėjimas greitai modeliuoti ir išbandyti naujus dizainus pagreitina kūrimo procesą, sukeliantį greitesnes naujoves ir sutrumpino laiką iki rinkos.

Ekonominis efektyvumas

Kelių funkcijų integravimas į vieną FPGA sumažina papildomų atskirų komponentų poreikį, o tai gali sutaupyti išlaidų tiek viešųjų pirkimų, tiek surinkimo metu.Ši integracija taip pat supaprastina gamybos procesą ir gali sumažinti bendrą sistemos sudėtingumą, todėl sumažėja priežiūros ir atnaujinimo išlaidos, susijusios su produkto gyvavimo cikle.

Ilgalaikė parama

„EP20K100EFC324-1X“ pertvarkomas aspektas užtikrina, kad būtų galima atnaujinti aparatinę įrangą, kad būtų galima ištaisyti klaidas, pagerinti našumą ar pridėti naujas funkcijas nereikalaujant fizinės aparatūros pakeitimų.Ši ilgalaikė parama ir pritaikomumas apsaugo investicijas ir įgalina įrenginius išlikti aktualiems, nes atsiranda naujų standartų ir technologijų.

EP20K100EFC324-1X Pakuotės matmenys

EP20K100EFC324-1X yra FPGA iš „Altera“ „Apex-20ke®“ serijos, laikoma a 324 rutulio smulkaus kamuolio tinklelio masyvas (FBGA) paketas.Jo pakuočių matmenys yra šie:

• Žingsnis: 1 mm

• Ilgis × plotis: 19 mm × 19 mm

• Plotas: 361 mm²

EP20K100EFC324-1X Gamintojas

„EP20K100EFC324-1X“ yra modelis iš „Apex-20ke®“ lauko programuojamų vartų matricų (FPGA), kurią iš pradžių sukūrė „Altera“.Po „Intel“ įsigijusios „Altera“ 2015 m., Šis FPGA ir kiti „Altera“ produktai tapo „Intel“ plataus programuojamų sprendimų portfelio dalimi.Dėl to „Intel“ Toliau palaiko „Altera“ produktų linijas, integruodama jas į savo pažangias technologijų pasiūlymus.Nors „EP20K100EFC324-1X“ buvo klasifikuojamas kaip pasenęs ir nebėra gaminamas, jo palikimas palaikomas naudojant „Intel“, kuriame rekomenduojami naujesni FPGA modeliai dabartinėms programoms, kad būtų užtikrintas ilgalaikis palaikymas ir prieinamumas.

Išvada

„EP20K100EFC324-1X“ yra galinga ir lanksti FPGA, leidžianti kurti ir išbandyti pasirinktines skaitmenines grandines.Tai siūlo aukštą našumą, įmontuotą atmintį ir daugialypės įtampos palaikymą, todėl ji yra naudinga daugelyje pramonės šakų.Šis vadovas perėmė pagrindines funkcijas, dizainą ir veiksmus, kaip paprasčiau programuoti šią FPGA, kad galėtumėte lengvai suprasti ir naudoti.

Duomenų lapas PDF

EP20K100EFC324-1X duomenų lapai:

Apie mus

ALLELCO LIMITED

Skaityti daugiau

Greitas užklausa

Prašau atsiųsti užklausą, mes nedelsdami atsakysime.

Dažnai užduodami klausimai [FAQ]

1. Kaip EP20K100EFC324-1X palyginamas su naujesniais FPGA modeliais?

EP20K100EFC324-1X išlieka galinga FPGA senosioms sistemoms ir pramoninėms reikmėms, kurioms reikalingas didelis loginis tankis ir lanksčios I/O galimybės.Tačiau, palyginti su šiuolaikinėmis FPGA, pavyzdžiui, „Intel's Cyclone“, „Arria“ ar „Stratix“ serijomis, jai trūksta pažengusio energijos efektyvumo, greitųjų siųstuvų ir AI varomo pagreičio.Jei kuriate naują sistemą, galime pasiūlyti lygiaverčius ar patobulintus modelius.

2. Ar EP20K100EFC324-1X palaiko išorines atminties sąsajas, tokias kaip DDR ar SRAM?

Taip, EP20K100EFC324-1X palaiko išorines atminties sąsajas, įskaitant SRAM ir SDRAM.Tačiau jis natūraliai nepalaiko DDR2/DDR3.Jei reikalinga greitaeigė atminties sąsaja, gali prireikti papildomos išorinės logikos arba naujesnės FPGA.

3. Ar galiu kelis kartus pertvarkyti EP20K100EFC324-1X?

Taip, kaip ir visi FPGA, šis įrenginys yra visiškai perprogramuojamas.Tačiau jei naudojant lakiąją konfigūraciją, jums reikės išorinės atminties (pvz., Serijinio prom), kad išlaikytumėte dizainą po maitinimo dviračių.

4. Ar galiu užprogramuoti EP20K100EFC324-1X, naudojant „Intel Quartus“ programinę įrangą?

Taip, galite užprogramuoti EP20K100EFC324-1X naudodami „Intel Quartus II“ (senas versijas), nes ši FPGA priklauso APEX-20KE® šeimai.Įsitikinkite, kad jūsų „Quartus II“ versija palaiko šį įrenginį, nes naujesni „Quartus Prime Editions“ nepalaiko senųjų FPGA.

5. Kokius maitinimo šaltinio reikalavimus turėčiau atsižvelgti naudodamas EP20K100EFC324-1X?

EP20K100EFC324-1X veikia su šerdies įtampos diapazonu nuo 1,71 V iki 1,89 V.Jame taip pat yra „Multivolt ™ I/O“ technologija, palaikanti 1,8 V, 2,5 V, 3,3 V ir 5,0 V loginius lygius.Įsitikinkite, kad jūsų maitinimo šaltinis atitinka šiuos įtampos reikalavimus stabiliam našumui.

XCV200-6FG456C FPGA: funkcijos, specifikacijos, programavimas ir programos

2025/03/20

Kodėl 0603 komponentai yra populiarūs šiuolaikinėje elektronikoje

2025/03/20

Populiarūs įrašai

-

Sudėtingos instrukcijos Nustatykite kompiuterius: kaip jie pakeitė skaičiavimą?

8000/04/18 147778

-

USB-C PINOUT ir funkcijos

2000/04/18 112027

-

„Xilinx Unified“ modeliavimo primityvų naudojimas: išsamus FPGA projektavimo ir modeliavimo vadovas

1600/04/18 111351

-

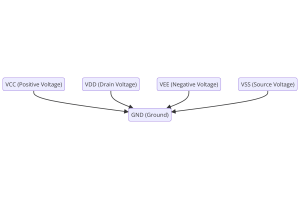

Maitinimo įtampa elektronikoje: VCC, VDD, VEE, VSS ir GND reikšmė

0400/04/18 83780

-

„RJ45“ jungties vadovas: „Pmout“, laidų, laidų tipai ir naudojimas

1970/01/1 79578

-

Pagrindinis vielos spalvų kodų vadovas šiuolaikinėse elektrinėse sistemose

Tai, kaip mūsų elektros sistemos naudoja spalvas, nėra tik išvaizdos.Kiekviena vielos spalva dabar rodo konkrečią funkciją, todėl montavimo ir priežiūros metu lengviau nustatyti ir tvarkyti elektro...1970/01/1 66971

-

Išvalymo vožtuvo vadovas: funkcija, simptomai, testavimas ir pakeitimas, kad būtų galima optimaliai atlikti variklio veikimą

Išvalymo vožtuvas yra pagrindinė automobilio sistemos dalis, padedanti išlaikyti orą švarų, valdant degalų garus, kol jie gali ištrūkti į atmosferą.Tai ne tik padeda aplinkai sumažinti taršą, bet i...1970/01/1 63107

-

Kokybės (Q) faktorius: lygtys ir programos

Kokybės koeficientas, arba „Q“, yra svarbus tikrinant, kaip gerai induktoriai ir rezonatoriai veikia elektroninėse sistemose, kuriose naudojami radijo dažniai (RF).„Q“ matuoja, kaip gerai grandinė ...1970/01/1 63041

-

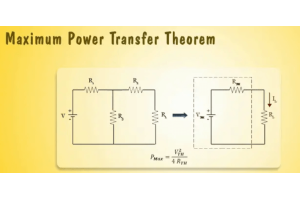

Pasiekti maksimalų našumą naudojant maksimalios galios perdavimo teoremą

Maksimalios galios perdavimo teorema paaiškina, kaip energija iš šaltinio, pavyzdžiui, akumuliatorius ar generatorius, teka į prijungtą apkrovą.Tai parodo tikslią sąlygą, kai apkrova gauna daugiaus...1970/01/1 54097

-

A23 akumuliatoriaus specifikacijos ir suderinamumas

„A23“ baterija yra maža, cilindro formos akumuliatorius, turintis aukštą įtampą.Taip pat vadinamas 23A, 23AE arba MN21, jis veikia esant 12 voltų ir daug aukštesnis nei AA ar AAA baterijos...1970/01/1 52191