XCV200-6FG456C FPGA: funkcijos, specifikacijos, programavimas ir programos

„XCV200-6FG456C“ yra galinga FPGA (lauko programuojama vartų masyvas) iš AMD Xilinx Virtex® serijos.Šis vadovas paaiškina jo funkcijas, PIN išdėstymo išdėstymą, programavimo veiksmus ir naudojimą.Ši FPGA padeda sukurti greitas ir patikimas skaitmenines sistemas, turint didelę apdorojimo galią, lanksčias projektavimo galimybes ir stiprias įvesties/išvesties (I/O) galimybes.Nesvarbu, ar dirbate prie tinklų, valdymo sistemų ar pasirinktinės elektronikos, šis vadovas padės suprasti, kaip XCV200-6FG456C gali būti naudojamas jūsų projektuose.Katalogas

XCV200-6FG456C apžvalga

XCV200-6FG456C yra pastebimas modelis AMD Xilinx Virtex® FPGA šeimoje, skirtas pateikti tvirtus programuojamus loginius sprendimus sudėtingoms skaitmeninėms sistemoms.Šis specifinis lustas apima maždaug 236 666 sistemos vartus ir turi 1,176 konfigūruojamus loginius blokus (CLB) ir 5 292 logines ląsteles.Tai taip pat apima 57 344 iš viso RAM bitų ir palaiko 284 I/O kaiščius, patalpintus 456 rutulio smulkiojo kamuolio rutulinio tinklo masyvo (FBGA) pakuotėje, kurio matmenys yra 23 mm x 23 mm.Šis modelis veikia 2,5 V nominalioje įtampoje, kurio diapazonas yra nuo 2,375 V iki 2,625 V, ir gali veikti temperatūros diapazone nuo 0 ° C iki 85 ° C.Platesnė „Virtex®“ serija patenkina įvairias programas, kurių tankis yra nuo 50 000 iki daugiau nei 1 milijono sistemos vartų, o sistemos laikrodžio rodikliai - iki 200 MHz.Tai palaiko daugybę I/O standartų, įskaitant LVTTL, LVCMOS ir PCI, be kita ko.Funkcijos, tokios kaip uždelsimo užrakintos kilpos (DLL), konfigūruojami loginiai blokai su įterpta atmintimi ir speciali aritmetinių operacijų nešiojimo logika padidina jo funkcionalumą.Pagaminta naudojant 0,22 μm 5 sluoksnių metalo procesą, „Virtex®“ šeima garantuoja našumą ir patikimumą.

Jei norite integruoti aukščiausios pakopos FPGA technologiją į savo produktus ar sistemas, pirkti „XCV200-6FG456C“ su mumis yra protingas žingsnis.Tai atitinka pramonės standartus ir neleidžia jums ateities technologijų poreikių.

XCV200-6FG456C funkcijos

• Sistemos vartai: „XCV200-6FG456C“ siūlo maždaug 236 666 sistemos vartus.Šis aukštas vartų skaičius leidžia įdiegti sudėtingas integruotas skaitmeninės logikos grandines ant vieno lusto, padidinant našumą ir universalumą įvairiose programose.

• Loginiai ištekliai: Tai apima 1,176 konfigūruojamus loginius blokus (CLB) ir 5 292 logines ląsteles.Šie ištekliai yra tinkami projektuoti lanksčias ir keičiamas skaitmenines grandines.CLBS gali būti užprogramuotas atlikti daugybę loginių funkcijų, o didelis loginių ląstelių skaičius leidžia atlikti plačias logines operacijas ir procesus.

• Atmintis: Įrenginys suteikia 57 344 bitų RAM, paskirstytą tarp jo loginių blokų.Šis įterptasis RAM naudojamas programoms, kurioms reikalingas greitas ir efektyvus duomenų saugojimas ir gavimas, palaikant greitųjų duomenų operacijas, neatsiejamas nuo šiuolaikinių skaitmeninių sistemų.

• I/O galimybės: Su 284 įvesties/išvesties kaiščiais, XCV200-6FG456C palengvina plačias sąsajos galimybes.Šie I/O kaiščiai palaiko įvairius signalo standartus ir leidžia FPGA efektyviai bendrauti su kitais sistemos komponentais, tokiais kaip atminties įrenginiai, procesoriai ir periferiniai įrenginiai.

• Įtampos ir temperatūros diapazonas: Veikimas esant 2,5 V nominaliam įtampai, kurios diapazonas yra nuo 2,375 V iki 2,625 V, šis FPGA yra skirtas naudoti mažos galios sunaudojant, išlaikant tvirtą našumą.Jis gali veikti sankryžos temperatūros diapazone nuo 0 ° C iki 85 ° C, užtikrinant patikimumą skirtingomis aplinkos sąlygomis.

XCV200-6FG456C PIN funkcijos diagrama

XCV200-6FG456C PIN funkcijos diagrama yra struktūrizuotas FPGA PIN priskyrimų vaizdas, suskirstytas į skirtingas bankus (0 bankas į 7 banką).Kiekviena banko grupių smeigtukai atsižvelgiant į jų funkciją ir fizinį išdėstymą ant FPGA paketo.Numeravimo ir ženklinimo sistema atitinka tinklelio modelį, kai eilutės žymimos raidėmis (A, B, C ir kt.) Ir stulpeliais pagal skaičius (1, 2, 3 ir kt.), Kurie palengvina greitą konkrečių kaiščių identifikavimą.Šie bankai atitinka skirtingas įvesties/išvesties funkcijas, galią, žemę ir specialų signalo maršrutą.Smeigtukams priskiriami įvairios funkcinės grupės, įskaitant bendrosios paskirties I/O (GPIO), dažnai pažymėtus kaip „G“ (bendrą įvestį/išvestį), „V“ (įtampos tiekimas) ir „O“ (išvestis).Galios ir žemės smeigtukai yra aiškiai pažymėti, užtikrinant stabilų FPGA veikimą.Specialios paskirties kaiščiai, tokie kaip laikrodžio įėjimai, atstatymai ir valdymo signalai, identifikuojami su tokiais simboliais kaip „R“ arba „T.“Kai kurie kaiščiai taip pat atlieka specialius komunikacijos vaidmenis, įskaitant JTAG konfigūraciją ir spartų spartų laikymąsi, programavimui ir derinimui.

XCV200-6FG456C BLOCK diagrama

Įvesties/išvesties blokas

Diagrama žymi Įvesties/išvesties blokas (IOB) XCV200-6FG456C FPGA, kuri yra „Xilinx Virtex“ šeimos narys, struktūra.Diagramoje pateikiami pagrindiniai elementai, susiję su įvesties ir išvesties operacijomis, išryškindami duomenų srauto ir valdymo mechanizmus.Diagramos branduolyje trys D flip-flops yra naudojami norint užregistruoti įvesties, išvesties ir trijų būsenų valdymo signalus.Išvesties registrą kontroliuoja OCE (išvesties laikrodžio įjungimas) signalas, kuris nustato, kada išvesties duomenys yra užfiksuoti.Panašiai „Tri-State“ registrą kontroliuoja TCE („Tri-State“ laikrodžio įjungimas), įgalinantis arba išjungdamas išvesties buferį.Įvesties registras užfiksuoja gaunamus duomenis ir pritaiko programuojamą vėlavimą, prieš perduodant jį vidinei FPGA logikai per IBUF (įvesties buferis).OBUFT („Tri-State“ išvesties buferis) užtikrina, kad FPGA gali arba nutiesti signalą ant trinkelės (I/o kaiščio) arba sudėti jį į didelio sunkumo būseną, atsižvelgiant į valdymo logiką.Ant padėklo yra silpna vartininkų grandinė, kad būtų išlaikyta paskutinę žinomą loginę būseną, kai nėra aktyvaus vairuotojo, užkirsti kelią nenumatytoms plūduriuojančioms sąlygoms.Tam tikroms įvesties standartams, tokiems kaip SSTL ar HSTL, naudojama etaloninė įtampa (VREF), kuriems tinkamai veikiant reikia tikslaus įtampos lygio.Apskritai, ši IOB struktūra leidžia FPGA valdyti didelės spartos duomenų perdavimą, palaiko skirtingus I/O standartus ir suteikia lanksčią signalo laiko ir vientisumo kontrolę.

Pagrindinis/vergo nuoseklusis režimas

Pagrindinis/vergo nuoseklusis režimas „Block Diagram“ iliustruoja „Virtex FPGA“ konfigūracijos procesą, ypač XCV200-6FG456C, kai užprogramuota „Daisy“ grandinės konfigūracijoje naudojant nuoseklųjį EEPROM (XC1701L).Šioje sąrankoje vienas „Virtex“ įrenginys veikia kaip pagrindinis, valdantis konfigūracijos laikrodį (CCLK) ir nuosekliai perduodantį konfigūracijos duomenis į papildomus vergų FPGA grandinėje.„Master FPGA“ inicijuoja konfigūracijos procesą, patvirtindamas programos signalą, atkurdamas visus grandinės įrenginius.Kai inicijavimas bus baigtas, inIT signalas rodo pasirengimą, o konfigūracijos duomenys iš „Serial EEPROM“ (XC1701L) teka į pagrindinio FPGA DIN (duomenų) kaiščią.Pagrindinis FPGA skaito duomenis iš EEPROM ir persiunčia juos per „Dout“ (duomenis) į vėlesnius vergo FPGA, sinchronizuodamas duomenų perdavimą naudojant CCLK signalą.Padarytas signalas naudojamas norint parodyti sėkmingą konfigūraciją, o pasirenkamas išsitraukimo rezistorius užtikrina stabilią aukštą būseną, kai konfigūracija bus baigta.„XC1701L EEPROM“ kontroliuoja pagrindinis FPGA, naudodamas CLK, duomenis, CE (Chip Enable) ir Reset/OE (išvesties įjungimo) signalus, užtikrinant, kad saugomi konfigūracijos duomenys būtų teisingai surinkti.Šis konfigūracijos metodas yra efektyvus norint programuoti kelis FPGA naudojant vieną EEPROM, sumažinant išorinį laidų sudėtingumą ir užtikrinant, kad visi įrenginiai gautų sinchronizuotus konfigūracijos duomenis.

XCV200-6FG456C specifikacijos

|

Tipas |

Parametras |

|

Gamintojas |

AMD Xilinx

|

|

Serija |

„Virtex®“ |

|

Pakuotė |

Dėklas |

|

Dalies būsena |

Pasenęs |

|

Laboratorijų/CLB skaičius |

1176 |

|

Loginių elementų/ląstelių skaičius |

5292 |

|

Iš viso RAM bitai |

57344 |

|

I/O skaičius |

284 |

|

Vartų skaičius |

236666 |

|

Įtampa - tiekimas |

2.375V ~ 2,625 V. |

|

Montavimo tipas |

Paviršiaus laikiklis |

|

Darbinė temperatūra |

0 ° C ~ 85 ° C (TJ) |

|

Paketas / atvejis |

456-BBGA |

|

Tiekėjo įrenginių paketas |

456-FBGA (23x23) |

|

Bazinis produkto numeris |

XCV200 |

XCV200-6FG456C programos

Telekomunikacijos ir tinklų kūrimas

„XCV200-6FG456C“ išsiskiria telekomunikacijų ir tinklų programomis, nes jos gebėjimas tvarkyti greitųjų duomenų perdavimą ir sudėtingas signalo apdorojimo užduotis.Aukštas vartų skaičius ir patikimos I/O galimybės leidžia palaikyti tokias funkcijas kaip paketų apdorojimas, signalo moduliacija/demoduliacija ir klaidų taisymo protokolai.

Skaitmeninio signalo apdorojimas (DSP)

Idealiai tinka DSP programoms, ši FPGA gali atlikti greitus ir sudėtingus matematinius skaičiavimus, reikalingus garso ir vaizdo apdorojimo technologijose.Nesvarbu, ar tai daugialypės terpės sistemos, balso atpažinimo ar srautinio perdavimo paslaugos, „XCV200-6FG456C“ galingos apdorojimo galimybės ir įterpta atminties palaikymo efektyvus ir aukštos kokybės signalo apdorojimas.

Pramoninės kontrolės sistemos

Pramoninėje automatikoje „XCV200-6FG456C“ suteikia reikiamą našumą valdymo sistemoms ir automatizavimo tinklams valdyti.Dėl galimybės vienu metu atlikti kelias valdymo užduotis, tuo pačiu užtikrinant, kad atsakymo laikas yra tinkamas procesų valdymui, robotikai ir mašininiam matymui.

Medicinos instrumentai

FPGA tikslumas ir greitis yra puikūs medicininiame vaizdavime ir diagnostikos įrangoje, kur ji padeda apdoroti sudėtingus vaizdavimo programų, tokių kaip MRT, ultragarsą ir CT nuskaitymus, algoritmus.„XCV200-6FG456C“ galimybės užtikrina, kad ji gali sutvarkyti didelį duomenų pralaidumą ir sudėtingą apdorojimą, reikalingą šiuolaikinėms medicinos technologijoms.

XCV200-6FG456C Panašios dalys

XCV200-6FG456C programavimo veiksmai

XCV200-6FG456C programavimo veiksmai:

1. Dizaino įrašas

Pradinis FPGA programavimo etapas apima jūsų sistemos skaitmeninės logikos ir funkcionalumo apibrėžimą.Tai galima padaryti naudojant aparatinės įrangos aprašymo kalbas (HDLS), tokias kaip VHDL ar „Verilog“, kur rašote kodą, kuriame nurodoma, kaip FPGA apdoroja duomenis ir sąveikauja su kita aparatine įranga.Galima naudoti scheminius įvesties įrankius, kuriuos galima naudoti „FPGA Design“ programinėje įrangoje, tokioje kaip „Xilinx ISE“ ar „Vivado“.Šis metodas apima vizualinio logikos vaizdavimo sukūrimą, tempiant ir numetant komponentus, kurie kai kuriems atrodo intuityvesni nei rašymo kodas.

2. Sintezė

Kai dizainas bus baigtas, kitas žingsnis yra sintezė, kai toks įrankis kaip „Xilinx“ XST (Xilinx sintezės technologija) paverčia jūsų DTL kodą ar scheminį dizainą į tinklą.Šis tinklo sąrašas apibūdina grandinę pagal generinius skaitmeninius komponentus, tokius kaip loginiai vartai ir registrai.Sintezės procesas taip pat apima projektavimo optimizavimą siekiant atitikti našumo reikalavimus ir sumažinti išteklių naudojimą efektyviam FPGA veikimui.

3. Įgyvendinimas

Įdiegimo procesas prasideda vertimu, derinant jūsų dizainą su apribojimų failais, kuriuose nurodomi parametrai, tokie kaip laikrodžio dažniai ir PIN priskyrimai.Po vertimo žemėlapio etapas priskiria jūsų tinklo sąrašo elementus konkrečiems FPGA fiziniams ištekliams, pavyzdžiui, paieškos lentelėms (LUT) ir „Flip-Flops“.Tada išdėstymo ir maršruto parinkimo fazė nustato fizines kiekvieno FPGA architektūros komponento vietas ir nustato ryšius tarp jų per programuojamus sujungimo išteklius.Šis etapas yra puikus norint pasiekti norimą našumo metriką, įskaitant laikrodžio dažnius.

4. Bitstream generavimas

Po sėkmingo išdėstymo ir nukreipimo įrankis sukuria „Bitstream“ - dvejetainį konfigūracijos failą, kuriame yra visa FPGA programavimo informacija.Dažnai rekomenduojama imituoti galutinį dizainą po suplapo, kad „Bitstream“ elgsis taip, kaip tikėtasi tokiomis sąlygomis.Šis patikrinimo žingsnis padeda išvengti galimų problemų realios operacijos metu.

5. Konfigūracija

Paskutinis žingsnis apima „BitsReam“ įkėlimą į FPGA naudojant įvairius konfigūracijos metodus.Vergo-serijos režimas, paprasta ir ekonomiška parinktis, sukonfigūruoja FPGA naudodamas išorinį pagrindinį įrenginį, kuris siunčia duomenis nuosekliai.Serialiniame režime FPGA autonomiškai nuskaito „Bitstream“ iš pridedamos serijos prom.Didelės spartos konfigūracijoms „SelectMap“ režimas leidžia išoriniam mikroprocesoriui greitai įkelti duomenis į FPGA.Be to, „JTAG“ režimas naudojamas ne tik programavimui, bet ir bandymams bei derinimui, naudojant standartinę sąsają sistemos programavimui ir ribų nuskaitymo testavimui.

XCV200-6FG456C pranašumai

Spektaklis

„Xilinx Virtex“ serija, kuriai priklauso XCV200-6FG456C, yra optimizuota greitaeigiai našumui, siūlanti sistemos laikrodžio rodiklius iki 200 MHz.Dėl to jis yra tinkamas programoms, kurioms reikalingas greitas duomenų apdorojimas, užtikrinant efektyvų sudėtingų algoritmų ir greitųjų operacijų, tokių kaip telekomunikacijos, apdorojimas ir daugialypės terpės, tvarkymas.

I/O standartų palaikymas

Ši FPGA palaiko platų įvesties/išvesties standartų spektrą, įskaitant LVTTL, LVCMOS, PCI, GTL, HSTL, SSTL, CTT ir AGP.Toks platus I/O standartų palaikymas leidžia „XCV200-6FG456C“ sklandžiai integruoti su įvairiais sistemos komponentais, padidindama jo naudingumą įvairiose skaitmeninėse ekosistemose.Šis lankstumas leidžia FPGA pritaikyti skirtingoms sąsajų sąlygoms be sistemos modifikacijų.

Laikrodžio valdymas

„XCV200-6FG456C“ apima kelias delsos užrakintas kilpas (DLL), skirtą laikrodžio paskirstymui ir valdymui sistemoje.Šie DLL padeda pagerinti sistemos laiką ir patikimumą, pateikiant tikslus laikrodžio signalus, reikalingus sinchroninėms operacijoms.Ši savybė yra svarbi mažinant sistemos klaidas ir sustiprinant bendrą našumą, ypač sudėtinguose dizainuose, reikalaujančiuose tikslaus laiko ir sinchronizacijos.

Dizaino lankstumas

Su 1,176 konfigūruojamais logikos blokais ir 5 292 loginėmis ląstelėmis „XCV200-6FG456C“ siūlo didelius loginius išteklius, turinčius galimybę įgyvendinti įvairius funkcionalumus.Nuo paprastos klijų logikos iki sudėtingų skaitmeninių sistemų, ši FPGA palaiko sudėtingus projektavimo reikalavimus, todėl jis yra idealus pritaikomoms programoms, skaitmeninio signalo apdorojimui ir prototipų kūrimui.

Greitas prototipų kūrimas

FPGA, kaip ir „XCV200-6FG456C“, garsėja dėl savo galimybių palaikyti greitą prototipų kūrimą.Šis įrenginys leidžia greitai suprojektuoti iteracijas ir gali būti pertvarkytas lauke, o tai yra vystymosi ciklų pranašumas, nes jis sumažina laiką iki rinkos.Tai taip pat efektyviai prisitaiko prie kintančių reikalavimų ar atnaujinimų projekto specifikacijose, užtikrinant, kad galutiniai produktai būtų atnaujinami pagal naujausius technologinius standartus.

Integracijos galimybės

„XCV200-6FG456C“ integracijos galimybės palengvina kelių atskirų komponentų konsolidavimą į vieną lustą.Ši integracija gali sumažinti sistemos sudėtingumą, sumažinti energijos suvartojimą ir sutaupyti išlaidas.Sumažindamas reikiamų atskirų komponentų skaičių, šis FPGA supaprastina projektavimo procesus ir pagerina visos sistemos patikimumą ir kompaktiškumą.

XCV200-6FG456C pakuočių matmenys

„XCV200-6FG456C“ yra lauko programuojamas vartų masyvas (FPGA) iš „AMD's Virtex®“ serijos, įsikūrusios 456 rutulio smulkiųjų rutulinių tinklelių masyvo (FBGA) pakete.

• Paketo tipas: 456-FBGA

• Pakuotės dydis: 23 mm x 23 mm

• Rutulio žingsnis: 1,0 mm

„XCV200-6FG456C“ gamintojas

„XCV200-6FG456C“ yra lauko programuojama vartų masyvas (FPGA), kurį iš pradžių sukūrė „Xilinx“, įmonė, žinoma dėl savo aukštos kokybės programuojamų loginių įrenginių.Po „Xilinx“ įsigijimo AMD, XCV200-6FG456C dabar yra susijęs su AMD kaip dabartiniu jo gamintoju.Tačiau šis FPGA modelis yra pasenęs ir nebe gaminamas.„AMD“ ir toliau palaiko naujesnes FPGA architektūras, pasižyminčias padidintu našumu, energijos efektyvumu ir ilgaamžiškumu, todėl šiuolaikinės alternatyvos yra tinkamos naujiems dizainams.

Išvada

„XCV200-6FG456C“ yra universalus ir greitas FPGA, naudingas daugeliui technologijų programų.Nors jis nebėra gaminamas, jis vis dar yra geras pasirinkimas senesnėms sistemoms, kurioms reikia patikimo našumo.Šis vadovas apėmė savo dizainą, programavimo veiksmus ir praktinį naudojimą, todėl lengviau suprasti, kaip jis veikia ir kaip jis gali būti naudojamas.Kai bus prieinami naujesni FPGA, galite naudoti šias žinias, kad pasirinktumėte tinkamą FPGA savo poreikiams ir patobulintumėte skaitmeninius dizainus.

Duomenų lapas PDF

XCV200-6FG456C duomenų lapai:

Apie mus

ALLELCO LIMITED

Skaityti daugiau

Greitas užklausa

Prašau atsiųsti užklausą, mes nedelsdami atsakysime.

Dažnai užduodami klausimai [FAQ]

1. Koks yra XCV200-6FG456C energijos suvartojimas?

„XCV200-6FG456C“ veikia esant 2,5 V, o įtampos diapazonas yra nuo 2,375 V iki 2,625 V.Energijos suvartojimas priklauso nuo loginio panaudojimo ir laikrodžio dažnio, tačiau, kaip senesnei FPGA, tai gali būti mažiau efektyvus energijai nei naujesni „Xilinx“ įrenginiai.Reikėtų atsižvelgti į tinkamą energijos valdymą ir šilumos išsklaidymą.

2. Kaip XCV200-6FG456C palyginamas su XCV200-6FG256C?

„XCV200-6FG456C“ turi didesnį paketą (456-Ball FBGA), palyginti su XCV200-6FG256C (256 kamuolių FBGA), siūlant daugiau I/O kaiščių (284 vs 172) ir galbūt geresnį našumą programoms, reikalaujančioms plačių sąsajų.Jei jūsų dizainas priklauso nuo daugiau I/O galimybių, geresnis pasirinkimas yra XCV200-6FG456C.

3. Ar galiu kelis kartus perprogramuoti XCV200-6FG456C?

Taip, „XCV200-6FG456C“ yra SRAM pagrįstas FPGA, tai reiškia, kad jis gali būti perprogramuotas neribotą skaičių kartų, kol tiekiama energija.Tačiau jums reikės išorinės nestabilios atminties (EEPROM arba „Flash“), kad išlaikytumėte „Bitstream“ po galios ciklo.

4. Ar „XCV200-6FG456C“ palaiko greitą serijinį ryšį?

„XCV200-6FG456C“ palaiko kelis I/O standartus, tokius kaip LVTTL, LVCMOS, PCI, GTL, HSTL ir SSTL, tačiau jame nėra įmontuotų greitųjų serdų (serializatorių/deserializatorių) ar schemų, tokių kaip modernūs FPGA.Programos, kurioms reikalingas greitas nuoseklias nuorodas (pvz., PCIE, Gigabit Ethernet ar HDMI), apsvarstykite naujesnius FPGA modelius.

5. Kaip „XCV200-6FG456C“ palyginamas su naujesniais FPGA modeliais?

„XCV200-6FG456C“ priklauso senesnės kartos FPGA.Palyginti su šiuolaikiniais „Virtex“ FPGA, jis turi mažesnį vartų skaičių, lėtesnį laikrodžio greitį ir ribotą energijos efektyvumą.Naujesni modeliai siūlo didesnį loginį tankį, labiau įterptą atmintį, patobulintus DSP blokus ir mažesnį energijos suvartojimą, todėl jie yra geresni šiuolaikinėms programoms.

AD73322AR PINOUT, SAVYBĖS IR TECHNO

2025/03/21

EP20K100EFC324-1X FPGA: funkcijos, specifikacijos, programos ir programavimo vadovas

2025/03/20

Populiarūs įrašai

-

Sudėtingos instrukcijos Nustatykite kompiuterius: kaip jie pakeitė skaičiavimą?

8000/04/18 147776

-

USB-C PINOUT ir funkcijos

2000/04/18 112019

-

„Xilinx Unified“ modeliavimo primityvų naudojimas: išsamus FPGA projektavimo ir modeliavimo vadovas

1600/04/18 111351

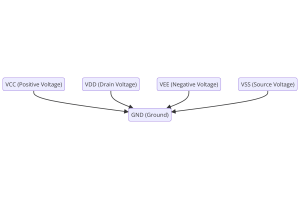

-

Maitinimo įtampa elektronikoje: VCC, VDD, VEE, VSS ir GND reikšmė

0400/04/18 83777

-

„RJ45“ jungties vadovas: „Pmout“, laidų, laidų tipai ir naudojimas

1970/01/1 79575

-

Pagrindinis vielos spalvų kodų vadovas šiuolaikinėse elektrinėse sistemose

Tai, kaip mūsų elektros sistemos naudoja spalvas, nėra tik išvaizdos.Kiekviena vielos spalva dabar rodo konkrečią funkciją, todėl montavimo ir priežiūros metu lengviau nustatyti ir tvarkyti elektro...1970/01/1 66964

-

Išvalymo vožtuvo vadovas: funkcija, simptomai, testavimas ir pakeitimas, kad būtų galima optimaliai atlikti variklio veikimą

Išvalymo vožtuvas yra pagrindinė automobilio sistemos dalis, padedanti išlaikyti orą švarų, valdant degalų garus, kol jie gali ištrūkti į atmosferą.Tai ne tik padeda aplinkai sumažinti taršą, bet i...1970/01/1 63104

-

Kokybės (Q) faktorius: lygtys ir programos

Kokybės koeficientas, arba „Q“, yra svarbus tikrinant, kaip gerai induktoriai ir rezonatoriai veikia elektroninėse sistemose, kuriose naudojami radijo dažniai (RF).„Q“ matuoja, kaip gerai grandinė ...1970/01/1 63041

-

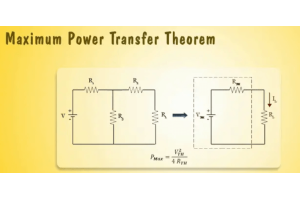

Pasiekti maksimalų našumą naudojant maksimalios galios perdavimo teoremą

Maksimalios galios perdavimo teorema paaiškina, kaip energija iš šaltinio, pavyzdžiui, akumuliatorius ar generatorius, teka į prijungtą apkrovą.Tai parodo tikslią sąlygą, kai apkrova gauna daugiaus...1970/01/1 54097

-

A23 akumuliatoriaus specifikacijos ir suderinamumas

„A23“ baterija yra maža, cilindro formos akumuliatorius, turintis aukštą įtampą.Taip pat vadinamas 23A, 23AE arba MN21, jis veikia esant 12 voltų ir daug aukštesnis nei AA ar AAA baterijos...1970/01/1 52189